УПРАВЛЕНИЕ СИЛОВЫМИ КЛЮЧАМИ ИМПУЛЬСНОГО БЛОКА ПИТАНИЯ

ПРИ ПОМОЩИ TL494

СТАТЬЯ ПОДГОТОВЛЕНА НА ОСНОВЕ КНИГИ А. В. ГОЛОВКОВА и В. Б ЛЮБИЦКОГО "БЛОКИ ПИТАНИЯ ДЛЯ СИСТЕМНЫХ МОДУЛЕЙ ТИПА IBM PC-XT/AT" ИЗДАТЕЛЬСТВА «ЛАД и Н»

УПРАВЛЯЮЩАЯ МИКРОСХЕМА TL494

В современных ИБП для формирования управляющего напряжения переключения мощных транзисторов преобразователя

обычно используются специализированные интегральные микросхемы (ИМС).

Идеальная управляющая ИМС для обеспечения нормальной работы ИБП в режиме ШИМ должна удовлетворять

большинству из перечисленных ниже условий:

• рабочее напряжение не выше 40В;

• наличие высокостабильного термостабилизи-рованного источника опорного напряжения;

• наличие генератора пилообразного напряже-

• обеспечение возможности синхронизации внешним сигналом программируемого плавного запуска;

• наличие усилителя сигнала рассогласования с высоким синфазным напряжением;

• наличие ШИМ-компаратора;

• наличие импульсного управляемого триггера;

• наличие двухканального предоконечного каскада с защитой от КЗ;

• наличие логики подавления двойного импульса;

• наличие средств коррекции симметрии выходных напряжений;

• наличие токоограничения в широком диапазоне синфазных напряжений, а также токоограничения

в каждом периоде с отключением в аварийном режиме;

• наличие автоматического управления с прямой передачей;

• обеспечение отключения при понижении напряжения питания;

• обеспечение защиты от перенапряжений;

• обеспечение совместимости с ТТЛ/КМОП логикой;

• обеспечение дистанционного включения и отключения.

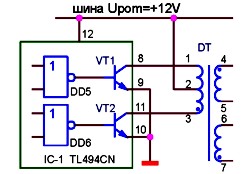

Рисунок 11. Управляющая микросхема TL494 и ее цоколевка.

В качестве схемы управления для рассматриваемого класса импульсных блоков питания в подавляющем большинстве случаев используется

микросхема типа TL494CN, выпускаемая фирмой TEXAS INSTRUMENT (США) (рис.11). Она реализует большинство

из перечисленных выше функций и выпускается рядом зарубежных фирм под разными наименованиями. Например,

фирма SHARP (Япония) выпускает микросхему IR3M02, фирма FAIRCHILD (США) - UA494, фирма SAMSUNG (Корея)

- КА7500, фирма FUJITSU (Япония) - МВ3759 и т.д. Все эти микросхемы являются полными аналогами отечественной

микросхемы КР1114ЕУ4. Рассмотрим подробно устройство и работу этой управляющей микросхемы. Она специально

разработана для управления силовой частью ИБП и содержит в своем составе (рис.12):

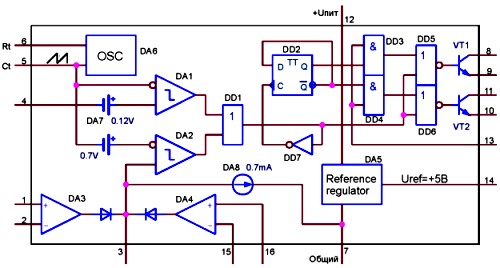

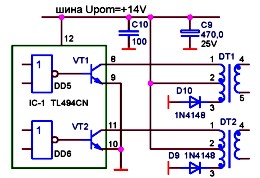

Рисунок 12. Функциональная схема ИМС TL494

• генератор пилообразного напряжения DA6; частота ГПН определяется номиналами резистора и конденсатора,

подключенных к 5-му и 6-му выводам, и в рассматриваемом классе БП выбирается равной примерно 60 кГц;

• источник опорного стабилизированного напряжения DA5 (Uref=+5,OB) с внешним выходом (вывод

14);

• компаратор "мертвой зоны" DA1;

• компаратор ШИМ DA2;

• усилитель ошибки по напряжению DA3;

• усилитель ошибки по сигналу ограничения тока DA4;

• два выходных транзистора VT1 и VT2 с открытыми коллекторами и эмиттерами;

• динамический двухтактный D-триггер в режиме деления частоты на 2 - DD2;

• вспомогательные логические элементы DD1 (2-ИЛИ), DD3 (2-Й), DD4 (2-Й), DD5 (2-ИЛИ-НЕ),

DD6 (2-ИЛИ-НЕ), DD7 (НЕ);

• источник постоянного напряжения с номиналом 0,1BDA7;

• источник постоянного тока с номиналом 0,7мА DA8.

Схема управления будет запускаться, т.е. на 8 и 11 выводах появятся последовательности импульсов

в том случае, если на вывод 12 подать любое питающее напряжение, уровень которого находится в диапазоне

от +7 до +40 В. Всю совокупность функциональных узлов, входящих в состав ИМС TL494, можно условно разбить

на цифровую и аналоговую часть (цифровой и аналоговый тракты прохождения сигналов). К аналоговой части

относятся усилители ошибок DA3, DA4, компараторы DA1, DA2, генератор пилообразного напряжения DA6, а также

вспомогательные источники DA5, DA7, DA8. Все остальные элементы, в том числе и выходные транзисторы, образуют

цифровую часть (цифровой тракт).

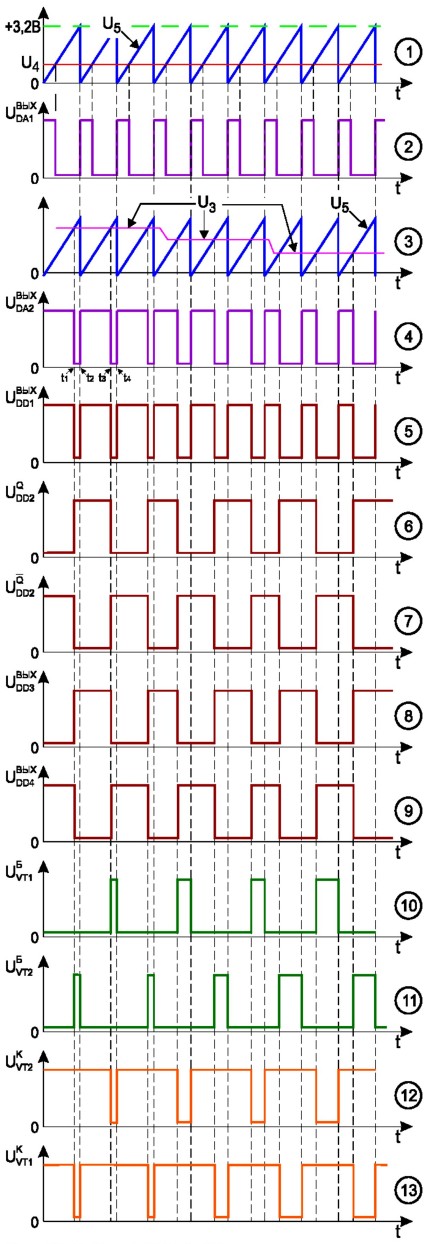

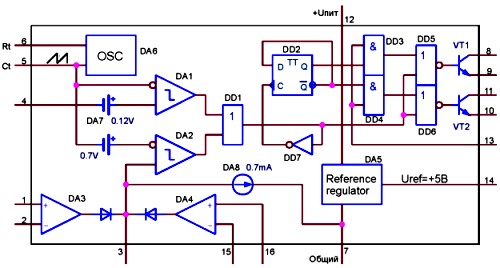

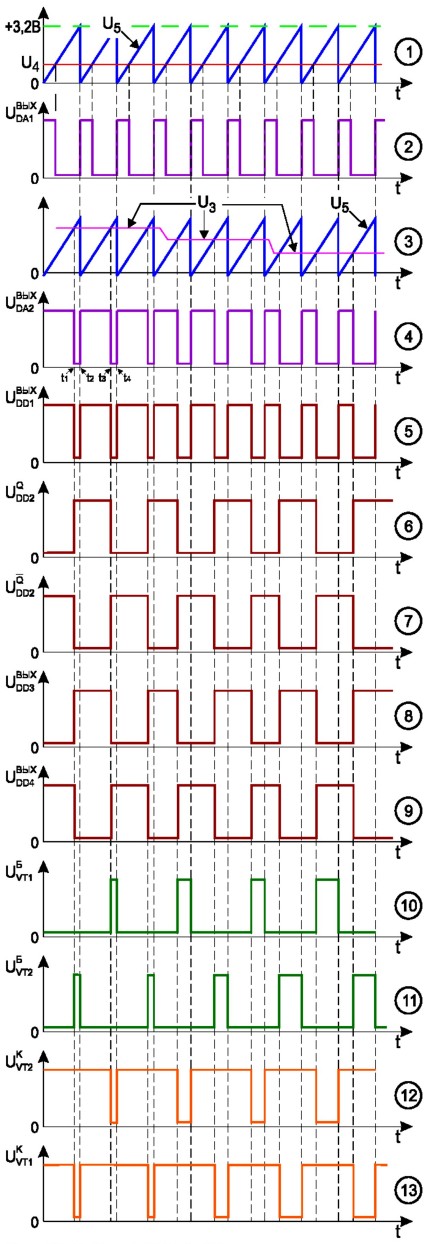

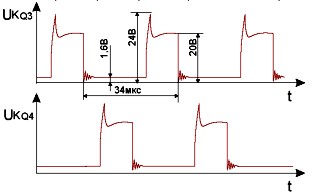

Рисунок 13. Работа ИМС TL494 в номинальном режиме: U3, U4, U5 - напряжения на выводах 3,

4, 5.

Рассмотрим в начале работу цифрового тракта. Временные диаграммы, поясняющие работу микросхемы, приведены

на рис. 13. Из временных диаграмм видно, что моменты появления выходных управляющих импульсов микросхемы,

а также их длительность (диаграммы 12 и 13) определяются состоянием выхода логического элемента DD1 (диаграмма

5). Остальная "логика" выполняет лишь вспомогательную функцию разделения выходных импульсов

DD1 на два канала. При этом длительность выходных импульсов микросхемы определяется длительностью открытого

состояния ее выходных транзисторов VT1, VT2. Так как оба эти транзистора имеют открытые коллекторы и эмиттеры,

то возможно двоякое их подключение. При включении по схеме с общим эмиттером выходные импульсы снимаются

с внешних коллекторных нагрузок транзисторов (с выводов 8 и 11 микросхемы), а сами импульсы направлены

выбросами вниз от положительного уровня (передние фронты импульсов отрицательны). Эмиттеры транзисторов

(выводы 9 и 10 микросхемы) в этом случае, как правило, заземляются. При включении по схеме с общим коллектором

внешние нагрузки подключаются к эмиттерам транзисторов и выходные импульсы, направленные в этом случае

выбросами вверх (передние фронты импульсов положительны), снимаются с эмиттеров транзисторов VT1, VT2.

Коллекторы этих транзисторов подключаются к шине питания управляющей микросхемы (Upom).

Выходные импульсы остальных функциональных узлов, входящих в состав цифровой части микросхемы

TL494, направлены выбросами вверх, независимо от схемы включения микросхемы.

Триггер DD2 является двухтактным динамическим D-триггером. Принцип его работы заключается

в следующем. По переднему (положительному) фронту выходного импульса элемента DD1 состояние входа D триггера

DD2 записывается во внутренний регистр. Физически это означает, что переключается первый из двух триггеров,

входя щих в состав DD2. Когда импульс на выходе элемента DD1 заканчивается, то по заднему (отрицательному)

фронту этого импульса переключается второй триггер в составе DD2, и состояние выходов DD2 меняется (на

выходе Q появляется информация, считанная со входа D). Это исключает возможность появления отпирающего

импульса на базе каждого из транзисторов VT1, VT2 дважды в течение одного периода. Действительно, пока

уровень импульса на входе С триггера DD2 не изменился, состояние его выходов не изменится. Поэтому импульс

передается на выход микросхемы по одному из каналов, например верхнему (DD3, DD5, VT1). Когда импульс

на входе С заканчивается, триггер DD2 переключается, запирает верхний и отпирает нижний канал (DD4, DD6,

VT2). Поэтому следующий импульс, поступающий на вход С и входы DD5, DD6 будет передаваться на выход микросхемы

по нижнему каналу. Таким образом каждый из выходных импульсов элемента DD1 своим отрицательным фронтом

переключает триггер DD2 и этим меняет канал прохождения следующего импульса. Поэтому в справочном материале

на управляющую микросхему указывается, что архитектура микросхемы обеспечивает подавление двойного импульса,

т.е. исключает появление двух отпирающих импульсов на базе одного и того же транзистора за период.

Рассмотрим подробно один период работы цифрового тракта микросхемы.

Появление отпирающего импульса на базе выходного транзистора верхнего (VT1) либо нижнего

(VT2) канала определяется логикой работы элементов DD5, DD6 ("2ИЛИ-НЕ") и состоянием элементов

DD3, DD4 ("2-И"), которое, в свою очередь, определяется состоянием триггера DD2.

Логика работы элемента 2-ИЛИ-НЕ, как известно, заключается в том, что на выходе такого элемента

появляется напряжение высокого уровня (логическая 1) в том лишь единственном случае, если на обоих его

входах присутствуют низкие уровни напряжений (логические 0). При остальных возможных комбинациях входных

сигналов на выходе элемента 2 ИЛИ-НЕ присутствует низкий уровень напряжения (логический 0). Поэтому если

на выходе Q триггера DD2 присутствует логическая 1 (момент ti диаграммы 5 рис.13), а на выходе /Q - логический

0, то на обоих входах элемента DD3 (2И) окажутся логические 1 и, следовательно, логическая 1 появится

на выходе DD3, а значит и на одном из входов элемента DD5 (2ИЛИ-НЕ) верхнего канала. Следовательно, независимо

от уровня сигнала, поступающего на второй вход этого элемента с выхода элемента DD1, состоянием выхода

DD5 будет логический О, и транзистор VT1 останется в закрытом состоянии. Состоянием же выхода элемента

DD4 будет логический 0, т.к. логический 0 присутствует на одном из входов DD4, поступая туда с выхода

/Q триггера DD2. Логический 0 с выхода элемента DD4 поступает на один из входов элемента DD6 и обеспечивает

возможность прохождения импульса через нижний канал. Этот импульс положительной полярности (логическая

1) появится на выходе DD6, а значит и на базе VT2 на время паузы между выходными импульсами элемента DD1

(т.е. на время, когда на выходе DD1 присутствует логический 0 - интервал trt2 диаграммы 5 рис.13). Поэтому

транзисгор VT2 открывается и на его коллекторе появляется импульс выбросом вниз от положительного уровня

(в случае включения по схеме с общим эмиттером).

Начало следующего выходного импульса элемента DD1 (момент t2 диаграммы 5 рис.13) не изменит

состояния элементов цифрового тракта микросхемы, за исключением элемента DD6, на выходе которого появится

логический 0, и поэтому транзистор VT2 закроется. Завершение выходного импульса DD1 (момент ta) обусловит

изменение состояния выходов триггера DD2 на противоположное (логический 0 - на выходе Q, логическая 1

- на выходе /Q). Поэтому поменяется состояние выходов элементов DD3, DD4 (на выходе DD3 - логический 0,

на выходе DD4 - логическая 1). Начавшаяся в момент !3 пауза на выходе элемента DD1 обусловит возможность

открывания транзистора VT1 верхнего канала. Логический 0 на выходе элемента DD3 "подтвердит"

эту возможность, превращая ее в реальное появление отпирающего импульса на базе транзистора VT1. Этот

импульс длится до момента U, после чего VT1 закрывается, и процессы повторяются.

Таким образом основная идея работы цифрового тракта микросхемы заключается в том, что длительность

выходного импульса на выводах 8 и 11 (либо на выводах 9 и 10) определяется длительностью паузы между выходными

импульсами элемента DD1. Элементы DD3, DD4 определяют канал прохождения импульса по сигналу низкого уровня,

появление которого чередуется на выходах Q и /Q триггера DD2, управляемого тем же элементом DD1. Элементы

DD5, DD6 представляют собой схемы совпадения по низкому уровню.

Для полноты описания функциональных возможностей микросхемы следует отметить еще одну важную

ее особенность. Как видно из функциональной схемы рисунке входы элементов DD3, DD4 объединены и выведены

на вывод 13 микросхемы. Поэтому если на вывод 13 подана логическая 1, то элементы DD3, DD4 будут работать

как повторители информации с выходов Q и /Q триггера DD2. При этом элементы DD5, DD6 и транзисторы VT1,

VT2 будут переключаться со сдвигом по фазе на половину периода, обеспечивая работу силовой части ИБП,

построенной по двухтактной полумостовой схеме. Если на вывод 13 будет подан логический 0, то элементы

DD3, DD4 будут заблокированы, т.е. состояние выходов этих элементов не будет изменяться (постоянный логический

0). Поэтому выходные импульсы элемента DD1 будут воздействовать на элементы DD5, DD6 одинаково. Элементы

DD5, DD6, а значит и выходные транзисторы VT1, VT2, будут переключаться без сдвига по фазе (одновременно).

Такой режим работы управляющей микросхемы используется в случае, если силовая часть ИБП выполнена по однотактной

схеме. Коллекторы и эмиттеры обоих выходных транзисторов микросхемы в этом случае объединяются с целью

умощнения.

В качестве "жесткой" логической единицы в двухтактных схемах используется выходное

напряжение

внутреннего источника микросхемы Uref (вывод 13 микросхемы объединяется с выводом 14).

Теперь рассмотрим работу аналогового тракта микросхемы.

Состояние выхода DD1 определяется выходным сигналом компаратора ШИМ DA2 (диаграмма 4), поступающим

на один из входов DD1. Выходной сигнал компаратора DA1 (диаграмма 2), поступающий на второй вход DD1,

не влияет в нормальном режиме работы на состояние выхода DD1, которое определяется более широкими выходными

импульсами ШИМ - компаратора DA2.

Кроме того, из диаграмм рис.13 видно, что при изменениях уровня напряжения на неинвертирующем

входе ШИМ компаратора (диаграмма 3) ширина выходных импульсов микросхемы (диаграммы 12, 13) будет пропорционально

изменяться. В нормальном режиме работы уровень напряжения на неинвертирующем входе компаратора ШИМ DA2

определяется только выходным напряжением усилителя ошибки DA3 (т.к. оно превышает выходное напряжение

усилителя DA4), которое зависит от уровня сигнала обратной связи на его неинвертирующем входе (вывод 1

микросхемы). Поэтому при подаче сигнала обратной связи на вывод 1 микросхемы ширина выходных управляющих

импульсов будет изменяться пропорционально изменению уровня этого сигнала обратной связи, который, в свою

очередь, изменяется пропорционально изменениям уровня выходного напряжения ИБП, т.к. обратная связь заводится

именно оттуда.

Промежутки времени между выходными импульсами на выводах 8 и 11 микросхемы, когда оба выходных

транзистора VT1 и VT2 ее закрыты, называются "мертвыми зонами".

Компаратор DA1 называется компаратором "мертвой зоны", т.к. он определяет минимально

возможную ее длительность. Поясним это подробнее.

Из временных диаграмм рис.13 следует, что если ширина выходных импульсов ШИМ-компа-ратора

DA2 будет в силу каких-либо причин уменьшаться, то начиная с некоторой ширины этих импульсов выходные

импульсы компаратора DA1 станут шире выходных импульсов ШИМ-компаратора DA2 и начнут определять состояние

выхода логического элемента DD1, а значит и. ширину выходных импульсов микросхемы. Другими словами, компаратор

DA1 ограничивает ширину выходных импульсов микросхемы на некотором максимальном уровне. Уровень ограничения

определяется потенциалом на неинвенти-рующем входе компаратора DA1 (вывод 4 микросхемы) в установившемся

режиме. Однако, с другой стороны, потенциал на выводе 4 будет определять диапазон широтной регулировки

выходных импульсов микросхемы. При увеличении потенциала на выводе 4 этот диапазон сужается. Самый широкий

диапазон регулировки получается тогда, когда потенциал на выводе 4 равен 0.

Однако в этом случае появляется опасность, связанная с тем, что ширина "мертвой зоны"

может стать равной 0 (например, в случае значительного возрастания потребляемого от ИБП тока). Это означает,

что управляющие импульсы на выводах 8 и 11 микросхемы будут следовать непосредственно друг за другом.

Поэтому может возникнуть ситуация, известная под названием "пробой по стойке". Она объясняется

инерционностью силовых транзисторов инвертора, которые не могут открываться и закрываться мгновенно. Поэтому,

если одновременно на базу открытого до этого транзистора подать запирающий сигнал, а на базу закрытого

транзистора - отпирающий (т.е. с нулевой "мертвой зоной"), то получится ситуация, когда один

транзистор еще не закрылся, а другой уже открыт. Тогда и возникает пробой по транзисторной стойке полумоста,

который заключается в протекании сквозного тока через оба транзистора. Ток этот, как видно из схемы рис.

5, минует первичную обмотку силового трансформатора и практически ничем не ограничен. Защита по току в

этом случае не работает, т.к. ток не протекает через токовый датчик (на схеме не показан; конструкция

и принцип действия применяемых токовых датчиков будут подробно рассмотрены в последующих разделах), а

значит, этот датчик не может выдать сигнал на схему управления. Поэтому сквозной ток достигает очень большой

величины за очень короткий промежуток времени. Это приводит к резкому возрастанию выделяющейся на обоих

силовых транзисторах мощности и практически мгновенному выходу их из строя (как правило, пробой). Кроме

того, броском сквозного тока могут быть выведены из строя диоды силового выпрямительного моста. Процесс

этот заканчивается перегоранием сетевого предохранителя, который из-за своей инерционности не успевает

защитить элементы схемы, а лишь защищает от перегрузки первичную сеть.

Поэтому управляющее напряжение; подаваемое на базы силовых транзисторов должно быть сформировано

таким образом, чтобы сначала надежно закрывался бы один из этих транзисторов, а уже потом открывался бы

другой. Другими словами, между управляющими импульсами, подаваемыми на базы силовых транзисторов обязательно

должен быть временной сдвиг, не равный нулю ("мертвая зона"). Минимальная допустимая длительность

"мертвой зоны" определяется инерционностью применяемых в качестве силовых ключей транзисторов.

Архитектура микросхемы позволяет регулировать величину минимальной длительности "мертвой

зоны" с помощью потенциала на выводе 4 микросхемы. Потенциал этот задается с помощью внешнего делителя,

подключаемого к шине выходного напряжения внутреннего опорного источника микросхемы Uref.

В некоторых вариантах ИБП такой делитель отсутствует. Это означает, что после завершения

процесса плавного пуска (см. ниже) потенциал на выводе 4 микросхемы становится равным 0. В этих случаях

минимально возможная длительность "мертвой зоны" все же не станет равной 0, а будет определяться

внутренним источником напряжения DA7 (0,1В), который подключен к неинвертирующему входу компаратора DA1

своим положительным полюсом, и к выводу 4 микросхемы - отрицательным. Таким образом, благодаря включению

этого источника ширина выходного импульса компаратора DA1, а значит и ширина "мертвой зоны",

ни при каких условиях не может стать равной 0, а значит "пробой по стойке" будет принципиально

невозможен. Другими словами, в архитектуру микросхемы заложено ограничение максимальной длительности ее

выходного импульса (минимальной длительности "мертвой зоны"). Если имеется делитель, подключенный

к выводу 4 микросхемы, то после плавного пуска потенциал этого вывода не равен 0, поэтому ширина выходных

импульсов компаратора DA1 определяется не только внутренним источником DA7, но и остаточным (после завершения

процесса плавного запуска) потенциалом на выводе 4. Однако при этом, как было сказано выше, сужается динамический

диапазон широтной регулировки ШИМ компаратора DA2.

СХЕМА ПУСКА

Схема пуска предназначена для получения напряжения, которым можно было бы запитать управляющую микросхему

с целью ее запуска после включения ИВП в питающую сеть. Поэтому под пуском подразумевается запуск в работу

в первую очередь управляющей микросхемы, без нормального функционирования которой невозможна работа силовой

части и всей схемы ИБП в целом.

Схема пуска может быть построена двумя различными способами:

• с самовозбуждением;

• с принудительным возбуждением.

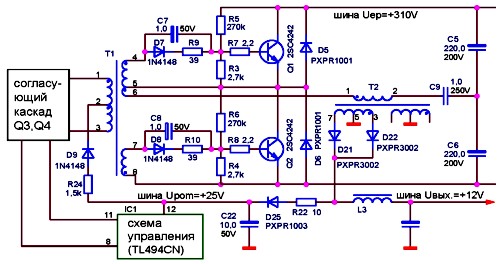

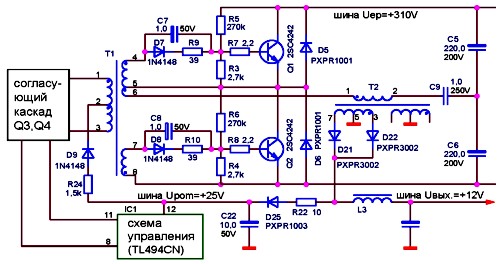

Схема с самовозбуждением используется, например, в ИБП GT-150W (рис.14). Выпрямленное напряжение

сети Uep подается на резистивный делитель R5, R3, R6, R4, являющийся базовым для обоих силовых ключевых

транзисторов Q1, Q2. Поэтому через транзисторы под воздействием суммарного напряжения на конденсаторах

С5, С6 (Uep) начинает протекать базовый ток по цепи (+)С5 - R5 - R7 - 6-э Q1 - R6 - R8 - 6-э Q2 - "общий

провод"первичной стороны - (-)С6.

Оба транзистора приоткрываются этим током. В результате через участки кол лектор-эмиттер

обоих транзисторов начинают протекать токи взаимно противоположных направлений по цепям:

• через Q1: (+)С5 - шина +310 В - к-э Q1 - 5-6 Т1 -1-2 Т2-С9- (-)С5.

• через Q2: (+)С6 - С9 - 2-1 Т2 - 6-5 Т1 - к-э Q2 -"общий провод"первичной стороны

- (-)С6.

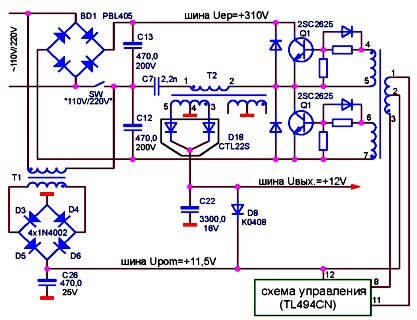

Рисунок 14. Схема запуска с самовозбуждением ИБП GT-150W.

Если бы оба тока, протекающие через дополнительные (пусковые) витки 5-6 Т1 в противоположных направлениях,

были бы равны, то результирующий ток был бы равен 0, и схема не смогла бы запуститься.

Однако в силу технологического разброса коэффициентов усиления по току транзисторов Q1,

Q2 всегда какой-либо один из этих токов больше другого, т.к. транзисторы приоткрыты в разной степени.

Поэтому результирующий ток через витки 5-6 Т1 не равен 0 и имеет то или иное направление. Допустим, что

преобладает ток через транзистор Q1 (то есть Q1 приоткрыт в большей степени, чем Q2) и, следовательно,

ток протекает в направлении от вывода 5 к выводу 6 Т1. Дальнейшие рассуждения основываются на этом допущении.

Однако, справедливости ради нужно отметить, что преобладающим может оказаться и ток через

транзистор Q2, и тогда все далее описываемые процессы будут относиться к транзистору Q2.

Протекание тока через витки 5-6 Т1 вызывает появление ЭДС взаимоиндукции на всех обмотках

управляющего трансформатора Т1. При этом (+)ЭДС возникает на выводе 4 относительно вывода 5 и в базу Q1

под воздействием этой ЭДС течет дополнительно приоткрывающий его ток по цепи: 4 Т1 - D7-R9-R7-6-3 Q1 -

5 Т1.

Одновременно на выводе 7 Т1 появляется (-) ЭДС относительно вывода 8, т.е. полярность этой

ЭДС оказывается запирающей для Q2 и он закрывается. Далее вступает в действие положительная обратная связь

(ПОС). Действие ее заключается в том, что при возрастании тока через участок коллектор-эмиттер Q1 и витки

5-6 Т1 на обмотке 4-5 Т1 действует возрастающая ЭДС, которая, создавая дополнительный базовый ток для

Q1, еще в большей степени приоткрывает его. Процесс этот развивается лавинообразно (очень быстро) и приводит

к полному открыванию Q1 и запиранию Q2. Через открытый Q1 и первичную обмотку 1-2 силового импульсного

трансформатора Т2 начинает протекать линейно нарастающий ток, что вызывает появление импульса ЭДС взаимоиндукции

на всех обмотках Т2. Импульс с обмотки 7-5 Т2 заряжает накопительную емкость С22. На С22 появляется напряжение,

которое подается в качестве питающего на вывод 12 управляющей микросхемы IC1 типа TL494 и на согласующий

каскад. Микросхема запускается и генерирует на своих выводах 11, 8 прямоугольные последовательности импульсов,

которыми через согласующий каскад (Q3, Q4, Т1) начинают переключаться силовые ключи Q1, Q2. На всех обмотках

силового трансформатора Т2 появляются импульсные ЭДС номинального уровня. При этом ЭДС с обмоток 3-5 и

7-5 постоянно подпитывают С22, поддерживая на нем неизменный уровень напряжения (около +27В). Другими

словами, микросхема по кольцу обратной связи начинает запи-тывать сама себя (самоподпитка). Блок выходит

на рабочий режим. Напряжение питания микросхемы и согласующего каскада является вспомогательным, действует

только внутри блока и обычно называется Upom.

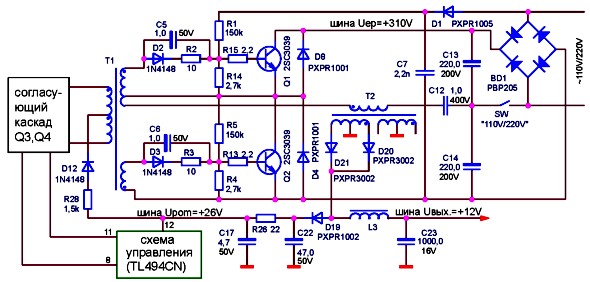

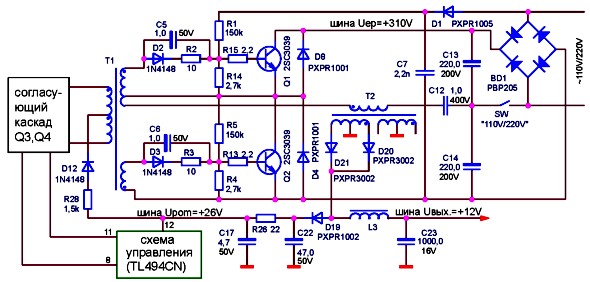

Эта схема может иметь некоторые разновидности, как например в импульсном блоке питания LPS-02-150XT

(производство Тайвань) для компьютера Мазовия СМ1914 (рис.15). В этой схеме начальный толчок для развития

процесса запуска получается с помощью отдельного однополупериодного выпрямителя D1, С7, который запитывает

в первый положительный полупериод сети базовый для силовых ключей резистивный делитель. Это ускоряет процесс

запуска, т.к. первоначальное отпирание одного из ключей происходит параллельно с зарядкой сглаживающих

конденсаторов большой емкости. В остальном схема работает аналогично рассмотренной выше.

Рисунок 15. Схема запуска с самовозбуждением в импульсном блоке питания LPS-02-150XT

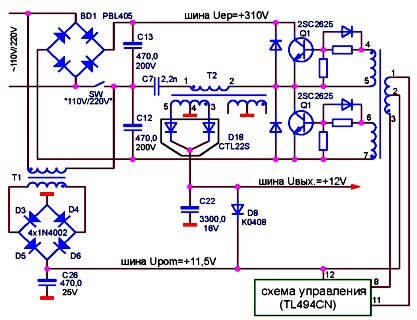

Такая схема используется, например, в ИБП PS-200B фирмы LING YIN GROUP (Тайвань).

Первичная обмотка специального пускового трансформатора Т1 включается на половинное напряжение

сети (при номинале 220В) либо на полное (при номинале 110В). Это делается из тех соображений, чтобы амплитуда

переменного напряжения на вторичной обмотке Т1 не зависела бы от номинала питающей сети. Через первичную

обмотку Т1 при включении ИБП в сеть протекает переменный ток. На вторичной обмотке 3-4 Т1 поэтому наводится

переменная синусоидальная ЭДС с частотой питающей сети. Ток, протекающий под воздействием этой ЭДС, выпрямляется

специальной мостовой схемой на диодах D3-D6 и сглаживается конденсатором С26. На С26 выделяется постоянное

напряжение около 10-11В, которое подается в качестве питающего на вывод 12 управляющей микросхемы U1 типа

TL494 и на согласующий каскад. Параллельно с этим процессом происходит заряд конденсаторов сглаживающего

фильтра. Поэтому к моменту подачи питания на микросхему силовой каскад также оказывается запитанным. Микросхема

запускается и начинает генерировать на своих выводах 8, 11 последовательности прямоугольных импульсов,

которыми через согласующий каскад начинают переключаться силовые ключи. В результате появляются выходные

напряжения блока. После выхода на режим самоподпитка микросхемы производится с шины выходного напряжения

+12В через развязывающий диод D8. Так как это напряжение самоподпитки немного превышает выходное напряжение

выпрямителя D3-D5, то диоды этого пускового выпрямителя запираются, и он в дальнейшем не влияет на работу

схемы.

Необходимость обратной связи через диод D8 не является обязательной. В схемах некоторых

ИБП, где применяется принудительное возбуждение, такая связь отсутствует. Управляющая микросхема и согласующий

каскад в течение всего времени работы запитываются с выхода пускового выпрямителя. Однако уровень пульсации

на шине Upom в этом случае получается несколько большим, чем в случае питания микросхемы с шины выходного

напряжения +12В.

Подводя итог описания схем запуска, можно отметить основные особенности их построения. В

схеме с самовозбуждением производится первоначальное переключение силовых транзисторов, результатом чего

является появление напряжения питания микросхемы Upom. В схеме с принудительным возбуждением сначала получают

Upom, а уже как результат - переключение силовых транзисторов. Кроме того, в схемах с самовозбуждением

напряжение Upom обычно имеет уровень около +26В, а в схемах с принудительным возбуждением - около +12В.

Схема с принудительным возбуждением (с отдельным трансформатором) приведена на рис.16.

Рисунок 16. Схема запуска с принудительным возбуждением импульсного блока питания PS-200B

(LING YIN GROUP).

СОГЛАСУЮЩИЙ КАСКАД ИМПУЛЬСНОГО БЛОКА ПИТАНИЯ

Для согласования и развязки мощного выходного каскада от маломощных цепей управления служит согласующий

каскад.

Практические схемы построения согласующего каскада в различных ИБП можно разделить на два

основных варианта:

• транзисторный вариант, где в качестве ключей используются внешние транзисторы в дискретном

исполнении;

• бестранзисторный вариант, где в качестве ключей используются выходные транзисторы самой

управляющей микросхемы VT1, VT2 (в интегральном исполнении).

Кроме того, еще одним признаком, по которому можно классифицировать согласующие каскады,

является способ управления силовыми транзисторами полумостового инвертора. По этому признаку все согласующие

каскады можно разделить на:

• каскады с общим управлением, где управление обоими силовыми транзисторами производится

с помощью одного общего для них управляющего трансформатора, который имеет одну первичную и две вторичные

обмотки;

• каскады с раздельным управлением, где управление каждым из силовых транзисторов производится

с помощью отдельного трансформатора, т.е. в согласующем каскаде имеется два управляющих трансформатора.

Исходя из обеих классификаций согласующий каскад может быть выполнен одним из четырех способов:

• транзисторный с общим управлением;

• транзисторный с раздельным управлением;

• бестранзисторный с общим управлением;

• бестранзисторный с раздельным управлением.

Транзисторные каскады с раздельным управлением применяются редко, либо вообще не применяются.

Авторам не довелось столкнуться с таким вариантом исполнения согласующего каскада. Остальные три варианта

встречаются более или менее часто.

Во всех вариантах связь с силовым каскадом осуществляется трансформаторным способом.

При этом трансформатор выполняет две основные функции: усиления управляющего сигнала по

току (за счет ослабления по напряжению) и гальванической развязки. Гальваническая развязка необходима

потому, что управляющая микросхема и согласующий каскад находятся на вторичной стороне, а силовой каскад

- на первичной стороне ИБП.

Рассмотрим работу каждого из упомянутых вариантов согласующего каскада на конкретных примерах.

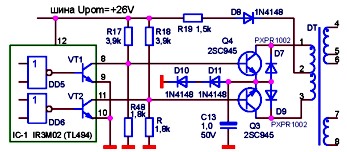

В транзисторной схеме с общим управлением в качестве согласующего каскада используется двухтактный

трансформаторный предварительный усилитель мощности на транзисторах Q3 и Q4 (рис.17).

Рисунок 17. Согласующий каскад импульсного блока питания KYP-150W (транзисторная схема с общим управлением).

Оба транзистора включены по схеме с общим эмиттером и работают в ключевом режиме. Коллекторными

нагрузками транзисторов являются первичные полуобмотки импульсного управляющего трансформатора DT и резистор

общей нагрузки R19, который задает максимальную величину тока через транзисторы (около 20мА). Напряжение

питания Upom подается в среднюю точку первичной обмотки через R19 и диод развязки D8. Транзисторы по отношению

к питающему напряжению включены параллельно.

На базы транзисторов Q3, Q4 поступают последовательности прямоугольных импульсов положительной

полярности с отрицательными передними фронтами, сдвинутые по фазе друг относительно друга на половину

периода. Из этого следует, что в промежутках между импульсами транзисторы Q3, Q4 открыты, т.к. к их управляющим

переходам приложено открывающее напряжение. Под воздействием управляющих импульсов транзисторы поочередно

закрываются.

На эмиттерах Q3, Q4 поддерживается напряжение примерно равное +1.6В за счет цепочки D10,

D11, С13. Это напряжение позволяет осуществлять активное попеременное закрывание обоих транзисторов. Действительно,

когда на базе закрываемого транзистора действует выходной импульс микросхемы, то напряжение на базе близко

к 0 (около +0.6В). Напряжение же на эмиттере за счет цепочки D10, D11, С13 постоянно поддерживается на

уровне +1.6В. Поэтому к управляющему переходу база-эмиттер на время действия выходного импульса микросхемы

оказывается приложенным в запирающей полярности напряжение около 1В. Фронты коллекторных импульсов в результате

получаются крутыми.

Диоды D7, D9 предназначены для гашения паразитных колебательных процессов, которые возникают

при запирании транзисторов Q3, Q4, в паразитном контуре, образованном первичной обмоткой DT и ее распределенной

межвитковой емкостью.

При этом гашение (демпфирование) происходит по истечении первого полупериода паразитного

колебания, когда полярность напряжения на паразитном контуре меняет-ся. Ток демпфирования при запирании

тран-зистора Q4 протекает по цепи: 3 DT - к-э Q3 -D7 - 1 DT. При запирании транзистора Q3 -по цепи: 1

DT-к-э<34-D9-3DT.

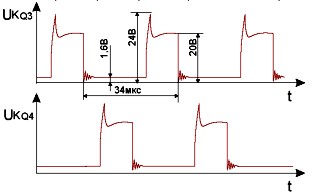

Первый полупериод этих паразитных высокочастотных колебаний выглядит как начальный выброс

напряжения на коллекторе транзистора при его запирании (рис.18).

Рисунок 18. Реальная форма импульсов на коллекторах

Токи через диоды D7 и D9, протекающие под воздействием магнитной энергии, запасенной в

сердечнике DT, имеют вид спадающей экспоненты. В сердечнике DT во время протекания токов через диоды D7

и D9 действует изменяющийся (спадающий) магнитный поток, что и обуславливает появление импульсов ЭДС на

его вторичных обмотках.

Диод D8 устраняет влияние согласующего каскада на управляющую микросхему через общую шину

питания.

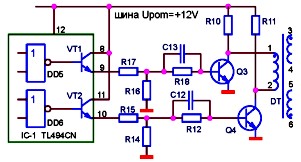

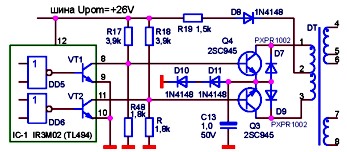

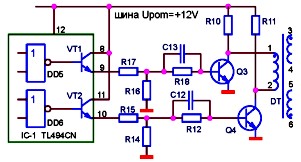

Другая разновидность транзисторного согласующего каскада с общим управлением используется

в импульсном блоке питания ESAN ESP-1003R (рис.19). Первой особенностью этого варианта является то, что

выходные транзисторы VT1, VT2 микросхемы включены как эмиттерные повторители. Выходные сигналы снимаются

с выводов 9, 10 микросхемы. Резисторы R17, R16 и R15, R14 являются эмиттер-ными нагрузками транзисторов

VT1 и VT2 соответственно. Эти же резисторы образуют базовые делители для транзисторов Q3, Q4, которые

работают в ключевом режиме. Емкости С13 и С12 являются форсирующими и способствуют ускорению процессов

переключения транзисторов Q3, Q4. Второй характерной особенностью этого каскада является то, что первичная

обмотка управляющего трансформатора DT не имеет вывода от средней точки и подключена между коллекторами

транзисторов Q3, Q4. Когда выходной транзистор VT1 управляющей микросхемы открывается, то оказывается

запитан напряжением Upom базовый для транзистора Q3 делитель R17, R16. Поэтому через управляющий переход

Q3 протекает ток, и он открывается. Ускорению этого процесса способствует форсирующая емкость С13, которая

обеспечивает подачу в базу Q3 отпирающего тока, в 2-2,5 раза превышающего установившееся значение. Результатом

открывания Q3 является то, что первичная обмотка 1-2 DT своим выводом 1 оказывается подключена к корпусу.

Так как второй транзистор Q4 заперт, то через первичную обмотку DT начинает протекать нарастающий ток

по цепи: Upom - R11 - 2-1 DT - к-э Q3 - корпус.

Рисунок 19. Согласующий каскад импульсного блока питания ESP-1003R ESAN ELECTRONIC CO., LTD (транзисторная

схема с общим управлением).

На вторичных обмотках 3-4 и 5-6 DT появляются импульсы ЭДС прямоугольной формы. Направление

намотки вторичных обмоток DT разное. Поэтому один из силовых транзисторов (на схеме не показано) получит

открывающий базовый импульс, а другой - закрывающий. Когда VT1 управляющей микросхемы резко закрывается,

то вслед за ним также резко закрывается и Q3. Ускорению процесса закрывания способствует форсирующая емкость

С13, напряжение с которой прикладывается к переходу база-эмиттер Q3 в закрывающей полярности. Далее длится

"мертвая зона", когда оба выходных транзистора микросхемы закрыты. Далее открывается выходной

транзистор VT2, а значит оказывается запитанным напряжением Upom базовый для второго транзистора Q4 делитель

R15, R14. Поэтому Q4 открывается и первичная обмотка 1-2 DT оказывается подключена к корпусу другим своим

концом (выводом 2), поэтому через нее начинает протекать нарастающий ток противоположного предыдущему

случаю направления по цепи: Upom -R10- 1-2 DT - к-э Q4 - "корпус".

Поэтому полярность импульсов на вторичных обмотках DT меняется, и открывающий импульс получит

второй силовой транзистор, а на базе первого будет действовать импульс закрывающей полярности. Когда VT2

управляющей микросхемы резко закрывается, то вслед за ним также резко закрывается Q4 (с помощью форсирующей

емкости С12). Далее опять длится "мертвая зона", после чего процессы повторяются.

Таким образом, основная идея, заложенная в работу этого каскада, заключается в том, что

переменный магнитный поток в сердечнике DT удается получить благодаря тому, что первичная обмотка DT подключается

к корпусу то одним, то другим своим концом. Поэтому через нее протекает переменный ток без постоянной

составляющей при однополярном питании.

В бестранзисторных вариантах согласующих каскадов ИБП в качестве транзисторов согласующего

каскада, как это было отмечено ранее, используются выходные транзисторы VT1, VT2 управляющей микросхемы.

В этом случае дискретные транзисторы согласующего каскада отсутствуют.

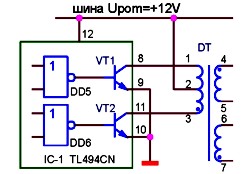

Бестранзисторная схема с общим управлением используется, например, в схеме ИБП PS-200В.

Выходные транзисторы микросхемы VT1, VT2 нагружаются по коллекторам первичными полуобмотками трансформатора

DT (рис.20). Питание подается в среднюю точку первичной обмотки DT.

Рисунок 20. Согласующий каскад импульсного блока питания PS-200B (бестранзисторная схема с общим управлением).

Когда открывается транзистор VT1, то нарастающий ток протекает через этот транзистор и

полуобмотку 1-2 управляющего трансформатора DT. На вторичных обмотках DT появляются управляющие импульсы,

имеющие такую полярность, что один из силовых транзисторов инвертора открывается, а другой закрывается.

По окончании импульса VT1 резко закрывается, ток через полуобмотку 1-2 DT перестает протекать, поэтому

исчезает ЭДС на вторичных обмотках DT, что приводит к закрыванию силовых транзисторов. Далее длится "мертвая

зона", когда оба выходных транзистора VT1, VT2 микросхемы закрыты, и ток через первичную обмотку

DT не протекает. Далее открывается транзистор VT2, и ток, нарастая во времени, протекает через этот транзистор

и полуобмотку 2-3 DT. Магнитный поток, создаваемый этим током в сердечнике DT, имеет противоположное предыдущему

случаю направление. Поэтому на вторичных обмотках DT наводятся ЭДС противоположной предыдущему случаю

полярности. В результате открывается второй транзистор полумостового инвертора, а на базе первого импульс

имеет закрывающую его полярность. Когда VT2 управляющей микросхемы закрывается, ток через него и первичную

обмотку DT прекращается. Поэтому исчезают ЭДС на вторичных обмотках DT, и силовые транзисторы инвертора

вновь оказываются закрыты. Далее опять длится "мертвая зона", после чего процессы повторяются.

Основная идея построения этого каскада заключается в том, что переменный магнитный поток

в сердечнике управляющего трансформатора удается получить благодаря подаче питания в среднюю точку первичной

обмотки этого трансформатора. Поэтому токи протекают через полуобмотки с одинаковым числом витков в разных

направлениях. Когда оба выходных транзистора микросхемы закрыты ("мертвые зоны"), магнитный

поток в сердечнике DT равен 0. Поочередное открывание транзисторов вызывает поочередное появление магнитного

потока то одной, то другой полуобмотки. Результирующий магнитный поток в сердечнике получается переменным.

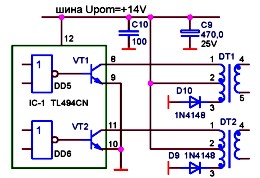

Последняя из указанных разновидностей (бестранзисторная схема с раздельным управлением)

используется, например, в ИБП компьютера Appis (Перу). В этой схеме имеется два управляющих трансформатора

DT1, DT2, первичные полуобмотки которых являются коллекторными нагрузками для выходных транзисторов микросхемы

(рис.21). В этой схеме управление каждым из двух силовых ключей осуществляется через отдельный трансформатор.

Питание подается на коллекторы выходных транзисторов микросхемы с общей шины Upom через средние точки

первичных обмоток управляющих трансформаторов DT1, DT2.

Диоды D9, D10 с соответствующими частями первичных обмоток DT1, DT2 образуют схемы размагничивания

сердечников. Остановимся на этом вопросе подробнее.

Рисунок 21. Согласующий каскад импульсного блока питания "Appis" (бестранзисторная схема с раздельным

управлением).

Согласующий каскад (рис.21) по сути представляет собой два независимых однотактных прямоходовых

преобразователя, т.к. открывающий ток протекает в базу силового транзистора во время открытого состояния

согласующего транзистора, т.е. согласующий и связанный с ним через трансформатор силовой транзистор открыты

одновременно. При этом оба импульсных трансформатора DT1, DT2 работают с постоянной составляющей тока

первичной обмотки, т.е. с вынужденным подмагничиванием. Если не предусмотреть специальных мер по размагничиванию

сердечников, то они войдут в магнитное насыщение за несколько периодов работы преобразователя, что приведет

к значительному уменьшению индуктивности первичных обмоток и выходу из строя переключающих транзисторов

VT1, VT2. Рассмотрим процессы, протекающие в преобразователе на транзисторе VT1 и трансформаторе DT1.

Когда транзистор VT1 открывается, через него и первичную обмотку 1-2 DT1 протекает линейно нарастающий

ток по цепи: Upom -2-1 DT1 - к-э VT1 - "корпус".

Когда отпирающий импульс на базе VT1 заканчивается, он резко закрывается. Ток через обмотку

1-2 DT1 прекращается. Однако ЭДС на размагничивающей обмотке 2-3 DT1 при этом меняет полярность, и через

эту обмотку и диод D10 протекает размагничивающий сердечник DT1 ток по цепи: 2 DT1 - Upom - С9- "корпус"-

D10-3DT1.

Ток этот - линейно спадающий, т.е. производная магнитного потока через сердечник DT1 меняет

знак, и сердечник размагничивается. Таким образом во время этого обратного такта происходит возврат избыточной

энергии, запасенной в сердечнике DT1 за время открытого состояния транзистора VT1, в источник (подзаряжается

накопительный конденсатор С9 шины Upom).

Однако такой вариант реализации согласующего каскада наименее предпочтителен, т.к. оба трансформатора

DT1, DT2 работают с недоиспользованием по индукции и с постоянной составляющей тока первичной обмотки.

Перемаг-ничивание сердечников DT1, DT2 происходит по частному циклу, охватывающему только положительные

значения индукции. Магнитные потоки в сердечниках из-за этого получаются пульсирующими, т.е. содержат

постоянную составляющую. Это приводит к завышенным массогабарит-ным показателям трансформаторов DT1, DT2

и, кроме того, по сравнению с другими вариантами согласующего каскада, здесь требуется два трансформатора

вместо одного.

Адрес администрации сайта: admin@soundbarrel.ru

|