МЯГКИЙ СТАРТ ИМПУЛЬСНОГО БЛОКА ПИТАНИЯ

СТАТЬЯ ПОДГОТОВЛЕНА НА ОСНОВЕ КНИГИ А. В. ГОЛОВКОВА и В. Б ЛЮБИЦКОГО "БЛОКИ ПИТАНИЯ ДЛЯ СИСТЕМНЫХ МОДУЛЕЙ ТИПА IBM PC-XT/AT" ИЗДАТЕЛЬСТВА «ЛАД и Н»

СХЕМА "МЕДЛЕННОГО ПУСКА"

При включении импульсного блока питания конденсаторы выходных фильтров еще не заряжены. Поэтому транзисторный

преобразователь работает фактически на коротко замкнутую нагрузку. При этом мгновенная мощность на коллекторных

переходах мощных транзисторов может превышать в несколько раз среднюю мощность, потребляемую от сети.

Это происходит из-за того, что действие обратной связи при запуске приводит к превышению тока транзисторов

по сравнению с допустимым. Поэтому необходимы меры обеспечения "плавного" ("мягкого" или "медленного")

пуска преобразователя. В рассматриваемых ИБП это достигается путем плавного увеличения длительности включенного

состояния мощных транзисторов вне зависимости от сигнала обратной связи, который "требует" от схемы управления

максимально возможной длительности управляющего импульса сразу при включении ИБП. Т.е. коэффициент заполнения

импульсного напряжения в момент включения принудительно делается очень малым и затем плавно увеличивается

до необходимого. "Медленный пуск" позволяет управляющей микросхеме IC1 постепенно увеличивать длительность

импульсов на выводах 8 и 11 до выхода БП в номинальный режим. Во всех ИБП на основе управляющей ИМС типа

TL494CN схема "медленного пуска" реализуется при помощи RC-цепочки, подключенной к неинвертирующему входу

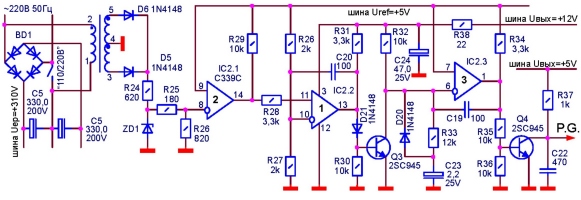

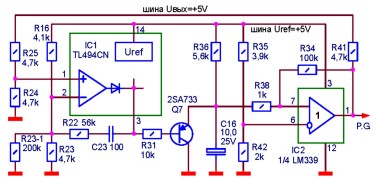

компаратора "мертвой зоны" DA1 (вывод 4 микросхемы). Рассмотрим работу схемы пуска на примере ИБП LPS-02-150XT

(рис.41). "Медленный пуск" осуществляется в данной схеме благодаря RC-цепочке С19, R20, подключенной к

выводу 4 управляющей микросхемы IC1.

Прежде чем рассматривать работу схемы "мягкого пуска" необходимо ввести понятие

об алгоритме запуска ИБП. Под алгоритмом запуска подразумевается последовательность появления напряжений

в схеме ИБП. В соответствии с физикой работы первоначально всегда появляется выпрямленное напряжение сети

Uep. Затем, как результат срабатывания схемы пуска, появляется напряжение питания управляющей микросхемы

Upom. Результатом подачи питания на микросхему является появление выходного напряжения внутреннего стабилизированного

источника опорного напряжения Uref. Лишь только после этого появляются выходные напряжения блока. Последовательность

появления этих напряжений не может быть нарушена, т.е. Uref, например, не может появиться раньше, чем

Upom и т.д.

Примечание Обращаем Ваше особое внимание на то, что процесс первоначального запуска ИБП

и процесс "медленного пуска" - это разные процессы, протекающие последовательно во времени!

При включении ИБП в сеть сначала происходит первоначальный запуск, а уже потом - "медленный пуск",

облегчающий силовым транзисторам блока выход в номинальный режим.

Как уже отмечалось, конечной целью процесса "медленного пуска" является получение

плавно нарастающих по ширине выходных управляющих импульсов на выводах 8 и 11. Ширина выходных импульсов

определяется шириной импульсов на выходе логического элемента DD1 IC1 (см. рис.13). Протекание процесса

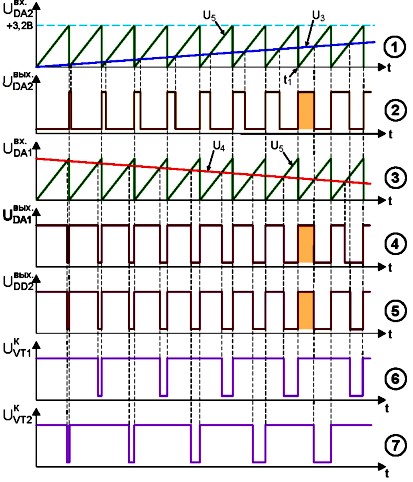

плавного запуска ИБП во времени показано на рис. 47.

Пусть в момент времени t0 на управляющую микросхему IC1 подается напряжение питания Upom.

В результате запускается генератор пилообразного напряжения DA6, и на выводе 14 появляется опорное напряжение

Uref. Пилообразное выходное напряжение генератора поступает на инвертирующие входы компараторов DA1 и

DA2. На инвертирующий вход ШИМ-компаратора DA2 подается выходное напряжение усилителя ошибки DA3. Так

как выходные напряжения блока (в том числе и +5В) еще отсутствуют, то сигнал обратной связи, снимаемый

с делителя R19, R20 и подаваемый на неинвертирующий вход усилителя ошибки, равен 0. На инвертирующий вход

этого усилителя подается некое положительное напряжение, снимаемое с делителя SVR, R24, R22 в цепи шины

опорного напряжения Uref, которое уже имеется. Поэтому выходное напряжение усилителя ошибки DA3 будет

равно 0 в первоначальный момент, а по мере заряда выходных конденсаторов фильтров - будет нарастать. Выходное

напряжение ШИМ-компаратора DA2 по этой причине будет представлять собой нарастающую по ширине последовательность

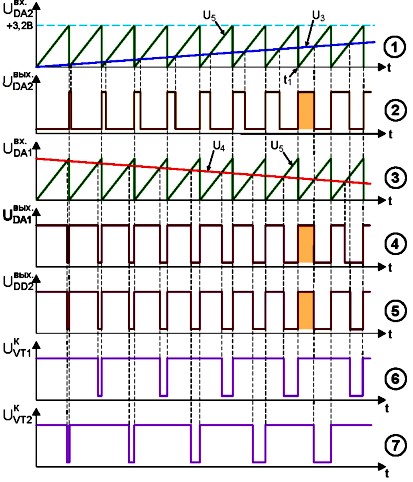

импульсов. Этот процесс отображен на временных диаграммах 1 и 2 (рис.47).

Рисунок 47. Временные диаграммы, поясняющие процесс плавного (мягкого) запуска ИБП и иллюстрирующие работу

управляющей HMCTL494 в пусковом режиме: U3,U4,U5 - напряжения на выводах ИМС 3, 4 и 5 соответственно.

Неинвертирующий вход компаратора "мертвой зоны" DA1, подключен к выводу 4 IC1.

К этому выводу подключается внешняя RC-цепь С19, R20, которая запитывается с шины опорного напряжения

Uref. Поэтому при появлении Uref все оно в первый момент выделяется на резисторе R20, т.к. конденсатор

С19 полностью разряжен. По мере заряда С19 ток через него и резистор R20 уменьшается. Поэтому падение

напряжения на R20, которое подается на вывод 4 1C 1, имеет форму спадающей экспоненты. В соответствии

с этим выходное напряжение компаратора "мертвой зоны" DA1 будет представлять собой последовательность

уменьшающихся по ширине импульсов. Этот процесс отображен на временных диаграммах 3 и 4 (рис,47). Таким

образом процессы широтного изменения выходных напряжений компараторов DA1 и DA2 имеют взаимно противоположный

характер.

Выходные напряжения компараторов являются входными для логического элемента DD1 (2-ИЛИ).

Поэтому ширина импульса на выходе этого элемента определяется наиболее широким из входных импульсов.

Из временной диаграммы 5 (рис. 47), отображающей выходное напряжение DD1, видно, что вплоть

до момента ti ширина выходных импульсов компаратора DA1 превышает ширину выходных импульсов ШИМ-компаратора

DA2. Поэтому переключения этого компаратора не влияют на ширину выходного импульса DD1, а значит и выходного

импульса IC1. Определяющим на интервале to-t-i является выходное напряжение компаратора DA1. Ширина выходных

импульсов IC1 на этом интервале плавно нарастает, что видно из временных диаграмм 6 и 7 (рис. 47).

В момент ti выходной импульс компаратора DA1 сравнивается по ширине с выходным импульсом

ШИМ-компаратора DA2. В этот момент происходит передача управления от компаратора DA1 к ШИМ-компаратору

DA2, т.к. его выходные импульсы начинают превышать по ширине выходные импульсы компаратора DA1. За время

t0-t, выходные конденсаторы фильтров успевают плавно зарядиться, и блок успевает выйти в номинальный режим.

Таким образом суть схемотехнического решения проблемы "мягкого" запуска заключается

в том, что на время зарядки конденсаторов выходных фильтров ШИМ-компаратор DA2 подменяется компаратором

DA1, работа которого не зависит от сигнала обратной связи, а определяется специальной формирующей RC-цепочкой

C19.R20.

Из рассмотренного выше материала следует, что перед каждым включением ИБП конденсатор формирующей

RC-цепи (в данном случае С19) должен быть полностью разряжен, иначе "мягкий" запуск будет невозможен,

что может привести к выходу из строя силовых транзисторов преобразователя. Поэтому в каждой схеме ИБП

предусмотрена специальная цепь для быстрого разряда конденсатора формирующей цепочки при выключении ИБП

из сети или при срабатывании токовой защиты.

СХЕМА ВЫРАБОТКИ СИГНАЛА PG (POWER GOOD)

Сигнал PG, наряду с четырьмя выходными напряжениями питания системного блока, является стандартным выходным

параметром ИБП.

Наличие этого сигнала является обязательным для любого блока, соответствующего стандарту

IBM (а не только блоков, построенных на основе микросхемы TL494). Однако в компьютерах класса XT этот

сигнал иногда не используется.

В ИБП встречается большое разнообразие вариантов схем выработки сигнала PG. Условно все

разнообразие схем можно разделить на две группы: од нефункциональные и двухфункциональные.

Од нефункциональные схемы реализуют только функцию задержки появления разрешающего запуск

процессора сигнала PG Н-уровня при включении ИБП.

Двухфункциональные схемы, кроме вышеуказанной функции, реализуют еще и функцию упреждающего

перехода сигнала PG в неактивный низкий уровень, запрещающий работу процессора при выключении ИБП, а также

в случаях возникновения различного рода аварийных ситуаций, прежде чем начнет уменьшаться питающее цифровую

часть системного модуля напряжение +5В.

Большинство схем выработки сигнала PG являются двухфункциональными, но при этом они являются

более сложными, чем схемы первого типа.

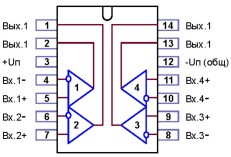

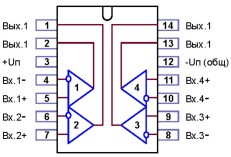

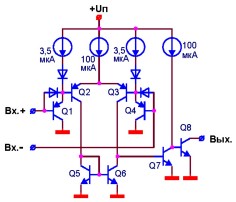

Рисунок 48. Функциональная схема ИМС LM339 (вид сверху).

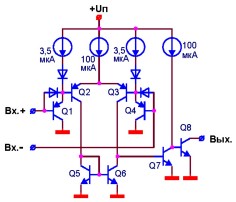

Рисунок 49. Принципиальная электрическая схема одного компаратора ИМС LM339.

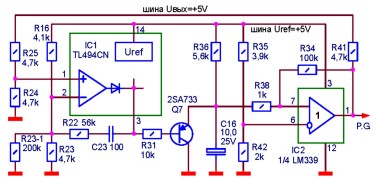

Рисунок 50. Схема образования сигнала PG в ИБП GT-200W

В качестве базового элемента при построении этих схем широко используется микросхема типа

LM339N, представляющая из себя счетверенный компаратор напряжения (рис. 48).

Выходные транзисторы каждого компаратора, имеют открытый коллектор (рис. 49). Вывод 12 LM339N

подключается к "корпусу", а на вывод 3 заводится однополярное (от +2В до +ЗОВ) питание.

Благодаря высокой чувствительности компа-раторных схем обеспечивается необходимое быстродействие.

Рассмотрим подробнее несколько характерных вариантов построения схем выработки сигнала PG.

Схема выработки сигнала PG, использованная в блоке GT-200W, показана на рис. 50.

Функция задержки при включении питания реализуется следующим образом.

При включении блока в сеть срабатывает схема пуска и на шине Uref появляется опорное напряжение

+5,1В от внутреннего источника микросхемы TL494. Выходное напряжение +5В еще отсутствует. Поэтому делитель

обратной связи R25, R24 еще не запитан (потенциал вывода 1 микросхемы равен 0В). Делитель же, дающий опорный

уровень на выводе 2 микросхемы, уже запитан напряжением Uref. Поэтому выходное напряжение усилителя ошибки

минимально (на выводе 3 потенциал около 0В), а запитанный по коллектору тем же напряжением Uref транзистор

Q7 открыт и насыщен током базы, протекающим по цепи: Uref - R36 - э-6 Q7 - R31 - внутренние цепи TL494

- "корпус".

Потенциал неинвертирующего входа компаратора 1 микросхемы IC2 (LM339N) равен 0, и, т.к.

на инвертирующем входе его присутствует положительный потенциал с резистора R42 делителя R35, R42 в цепи

Uref, сам компаратор будет находиться в состоянии 0В на выходе (выходной транзистор компаратора открыт

и насыщен). Поэтому сигнал PG имеет L-уровень и запрещает работу процессора.

Далее начинает появляться выходное напряжение +5В по мере зарядки выходных конденсаторов

большой емкости. Поэтому выходное напряжение усилителя ошибки DA3 начинает возрастать, а транзистор Q7

закрывается. Вследствие этого начинает заражаться задерживающая емкость С16. Ток зарядки протекает по

цепи: Uref -R36- С16- "корпус".

Как только напряжение на С16 и на неинвертирующем входе компаратора 1 (вывод 7 IC2) достигнет

опорного уровня на инвертирующем входе его (вывод 6 IC2), выходной транзистор компаратора закроется. ПОС,

которой охвачен компаратор 1 (резистор R34), обуславливает наличие гистерезиса на передаточной характеристике

этого компаратора. Этим обеспечивается надежность срабатывания схемы PG и исключается возможность "опрокидывания"

компаратора под воздействием случайной импульсной помехи (шума). На шине +5В к этому моменту появляется

полное номинальное напряжение» а сигнал PG становится сигналом Н-уровня.

Из вышеизложенного видно, что датчиком состояния блока (включен/отключен) в данной схеме

является выходное напряжение усилителя ошибки DA3, снимаемое с вывода 3 управляющей микросхемы IC1 (TL494),

а схема является одно-функциональной.

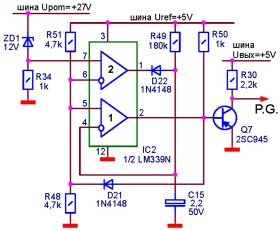

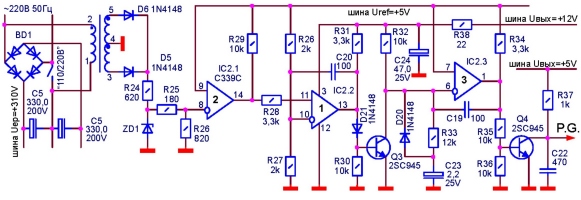

Более сложная схема выработки сигнала PG реализована в ИБП APPIS (рис. 51).

Рисунок 51. Схема образования сигнала PG в ИБП "Appis".

В этой схеме задействованы три компаратора микросхемы IC2.

Функция задержки при включении питания реализуется следующим образом.

После включения ИБП в сеть и срабатывания схемы пуска появляется опорное напряжение Uref.

Выходные напряжения блока еще отсутствуют. Поэтому микросхема IC2 и транзистор Q3 еще не запитаны. Транзистор

Q4, с коллектора которого снимается сигнал PG, открыт, т.к. запи-тан его базовый делитель. Ток базы протекает

по цепи: Uref- R34 - R35 -6-3Q4- "корпус".

Поэтому PG имеет L-уровень. Кроме того, с шины Uref происходит заряд конденсатора С21 по

цепи: Uref- R29- С21 - "корпус".

С появлением выходных напряжений блока с шины +12В через фильтр развязки R38, С24 запи-тываются

микросхема IC2 и транзистор Q3. С шины +5В запитывается по коллектору полным напряжением транзистор Q4.

При этом происходят следующие процессы.

На инвертирующий вход контролирующего компаратора начиная с момента включения блока поступает

несглаженное выпрямленное двухпо-лупериодной схемой D5, D6 напряжение со вторичной обмотки 3-4-5 специального

трансформатора Т1. Это пульсирующее напряжение с амплитудой около 15В подается на инвертирующий вход компаратора

2 через звено амплитудного ограничения R24, ZD1 (стабилитрон на 11В) и резистивный делитель R25, R26.

Так как амплитуда импульсов после ограничения и деления все же остается большей, чем уровень опорного

напряжения на неинвертирующем входе компаратора 2, то каждым импульсом и почти на все время его действия

компаратор 2 переводится в состояние 0В по выходу (выходной транзистор компаратора будет открыт). Поэтому

за несколько импульсов конденсатор задержки С21 разряжается практически до 0В. Поэтому компаратор 1 переключается

по выходу в состояние 0В, т.к. напряжение на неинвертирующем входе его определяется уровнем напряжения

на конденсаторе С21. В результате транзистор Q3 запирается нулевым смещением. Запирание Q3 приводит к

зарядке второго задерживающего конденсатора С23 по цепи: + 12В - R38 - R32 - R33 - С23 - "корпус".

Как только напряжение на коллекторе Q3, а следовательно, и на инвертирующем входе компаратора

3 достигнет порогового уровня на его инвертирующем входе (Uref=+5,1B), компаратор 3 переключится в состояние

0В на выходе (выходной транзистор компаратора открывается). Поэтому базовый для Q4 делитель R35, R36 окажется

незапитанным, и Q4 запрется.

Так как на шине +5В уже присутствует полное напряжение, a Q4 заперт, то сигнал PG становится

Н-уровия.

Функция упреждения при выключении питания реализуется следующим образом.

При выключении блока из сети сразу же перестает поступать выпрямленное напряжение со вторичной

обмотки 3-4-5 TL и схемы выпрямления D5, D6. Поэтому компаратор 2 сразу переключается, его выходной транзистор

закрывается. Далее начинает заряжаться от Uref через R29 емкость задержки С21. Этим предотвращается срабатывание

схемы при случайных кратковременных провалах сетевого напряжения. Когда С21 зарядится до половины напряжения

Uref, компаратор 1 переключится. Его выходной транзистор закроется. Тогда откроется транзистор Q3 током

базы, протекающем по цепи: +726 - R38 - R31 -D21-6-9Q3- "корпус".

Емкость второй задержки С23 быстро разряжается через Q3 и ускоряющий диод D20 по цепи: (+)С23

- D20 - к-э Q3 - "корпус"- (-)С23.

Потенциал инвертирующего входа компаратора 3 станет быстро уменьшаться со скоростью разряда

С23. Поэтому компаратор 3 переключится, выходной транзистор его закроется, и базовый делитель для Q4 оказывается

запитан с шины Uref. Поэтому Q4 откроется до насыщения, а сигнал PG станет L-уровня, предупреждая цифровую

часть системного блока о предстоящем исчезновении питающих напряжений.

Таким образом, в данной схеме датчиком состояния блока (включен/выключен) является наличие

или отсутствие трансформированного сетевого напряжения (через трансформатор Т1), а схема является двухфункциональной.

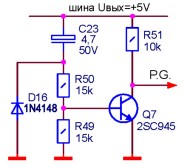

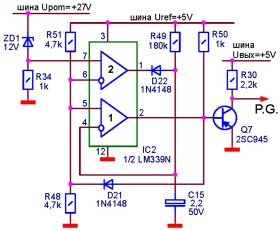

В блоке питания KYP-150W применена схема выработки сигнала PG с применением двух компараторов

микросхемы LM339N (рис. 52).

Рис. 52. Схема образования сигнала PG в ИБП KYP-150W (TUV ESSEN FAR EAST CORP.).

В данной схеме датчиком состояния блока является уровень вспомогательного напряжения питания

Upom микросхемы TL494.

Схема работает следующим образом. При включении ИБП в сеть срабатывает схема пуска, в результате

чего на шине Upon появляется напряжение, которым запитывается управляющая микросхема TL494. Как только

Upom достигнет уровня порядка +7В, микросхема запускается и на выводе 14 ее появляется выходное напряжение

внутреннего опорного источника Uref=+5B. Выходные напряжения блока еще отсутствуют. Микросхема IC2 (LM339N)

запитывается напряжением Uref по выводу 3.

Когда Upom достигнет уровня около +12В, "пробивается" стабилитрон ZD1, и на резисторе

R34 появляется падение напряжения, которое увеличивается с ростом Upom. Когда падение на R34 достигнет

уровня опорного напряжения на резисторе R48 делителя R51, R48 в цепи Uref, компаратор 2 микросхемы IC2

установится в состояние Н-уровня по выходу (выходной транзистор его закроется). Поэтому окажется заперт

диод D22. Начинается заряд задерживающей емкости С15 по цепи: Uref- R49- С15- "корпус"

Этот процесс вносит задержку "опрокидывания" компаратора 1 микросхемы IC2 и появления

разрешающего сигнала PG Н-уровня. За это время успевает произойти процесс "мягкого" запуска,

и выходные напряжения блока появляются в полном объеме, т.е. блок надежно выходит в номинальный режим.

Как только напряжение на С15 достигнет опорного уровня на резисторе R48, "опрокинется" компаратор

1. Его выходной транзистор откроется, и поэтому транзистор Q7 окажется заперт нулевым смещением. Сигнал

PG, снимаемый с коллекторной нагрузки Q7, станет Н-уровня, что позволит запуститься процессору системного

модуля.

При выключении блока из сети первым начинает исчезать напряжение Upom, т.к. накопительные

конденсаторы, поддерживающие напряжение на шине Uporn, имеют небольшую емкость. Как только падение напряжения

на резисторе R34 станет ниже опорного уровня на резисторе R48, компаратор 2 микросхемы IC2 переключится.

Выходной транзистор его откроется, и через него и диод D22 быстро разрядится емкость задержки С15. Разряд

происходит почти мгновенно, т.к. в цепи протекания тока разряда отсутствует ограничительное сопротивление.

Сразу вслед за этим переключится и компаратор 1 микросхемы IC2. ПОС через диод D21, охватывающая компаратор

1, обуславливает наличие гистерезиса на переходной характеристике компаратора. Выходной транзистор компаратора

закроется и током базы, протекающим по цепи: Uref - R50 - 6-э Q7 - "корпус", откроется транзистор

Q7. Сигнал PG станет L-уровня, предупреждая предстоящее исчезновение выходных напряжений блока. Таким

образом, данная схема является двухфункциональной.

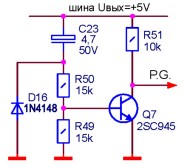

В ИБП GT-150W используется схема выработки сигнала PG, реализующая только функцию задержки

при включении (рис. 53).

Рисунок 53. Схема образования сигнала PG в ИБП GT-150W

После включения ИВП и срабатывания схемы пуска на выходных шинах блока начинают появляться

напряжения. Конденсатор С23 начинает заряжаться по цепи: шина +56 - С23 - R50 - 6-э Q7- "корпус".

Этим током открывается до насыщения транзистор Q7, с коллектора которого снимается сигнал

PG. Поэтому сигнал PG будет L-уровня почти все время зарядки С23. Как только напряжение на шине +5В перестанет

увеличиваться, достигнув номинального уровня, ток зарядки С23 перестает протекать. Поэтому Q7 закроется,

и сигнал PG станет сигналом Н-уровня.

Диод D16 необходим для быстрой и надежной разрядки С23 после выключения ИБП.

Таким образом схемы образования сигнала PG можно классифицировать по физическому принципу,

заложенному в основу их построения:

• схемы, построенные на основе контроля выходного напряжения внутреннего усилителя ошибки

по напряжению DA3 управляющей микросхемы или (что то же самое) контролирующие уровень сигнала обратной

связи с шины выходного напряжения +5В;

• схемы, построенные на основе контроля уровня и наличия переменного напряжения сети на

входе блока;

• схемы, построенные на основе контроля уровня вспомогательного напряжения питания управляющей

микросхемы Upom.

• схемы, построенные на основе контроля наличия импульсного переменного высокочастотного

напряжения на вторичной стороне силового импульсного трансформатора.

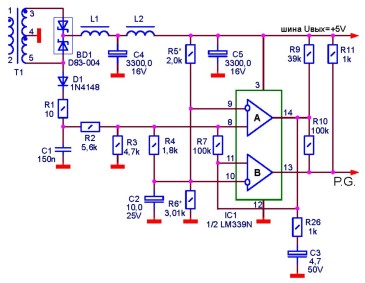

Рассмотрим один из вариантов реализации схемы последнего типа, которая используется, например,

в схеме ИБП HPR-200 (рис. 54). В основу построения этой схемы заложена идея контроля за наличием переменного

импульсного напряжения на вторичной обмотке силового импульсного трансформатора Т1. Схема работает следующим

образом.

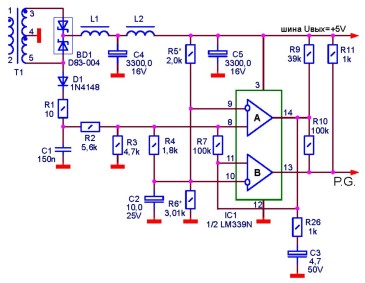

Рисунок 54. Схема образования сигнала PG в ИБП HPR-200 (HIGH POWER ELECTRONIC Co., Ltd)

При включении ИБП в сеть сглаживающие конденсаторы шины выходного напряжения +5В С4, С5

большой емкости (2хЗЗООмкф) полностью разряжены. Разряжены также конденсаторы С1, С2, СЗ. Импульсное переменное

напряжение, которое появляется на вторичной обмотке 3-5 силового импульсного трансформатора Т1, начинает

заряжать конденсаторы С4, С5. К отводу 5 вторичной обмотки подключен однополупериодный выпрямитель D1.

С1 - сглаживающая емкость фильтра. R1 (10 Ом) - токоограничивающий резистор. Конденсатор С1 малой емкости

(150нф) заряжается до уровня около +10В практически сразу (первым импульсом).

Как только уровень потенциала шины +5В превысит минимально допустимый уровень питающего

для микросхемы IC1 напряжения (+2В), микросхема начнет функционировать. Напряжение с конденсатора С1 подается

на резистивный делитель R2, R3. Часть этого напряжения снимается с R3 и подается на неинвертирующий вход

компаратора А (вывод 9 микросхемы IC1), а также на делитель R4, R6, С2. Поэтому параллельно с ростом потенциала

шины +5В происходит заряд конденсатора C2 по цепи: (+)C1 - R2 - R4 - C2 -"корпус"-(-)C1.

К моменту, когда потенциал шины +5В достигает минимального уровня питания микросхемы IC1

(+2В), этот конденсатор окажется заряженным. Поэтому компараторы микросхемы устанавливаются в следующее

состояние:

компаратор А - выходной транзистор закрыт, т.к. потенциал неинвертирующего входа выше потенциала

на инвертирующем входе;

компаратор В - выходной транзистор открыт, т.к. потенциал неинвертирующего входа ниже потенциала

на инвертирующем входе.

Такое распределение потенциалов обусловлено номиналами резисторов, подключенных ко входам

компараторов.

Сигнал PG, снимаемый с коллекторной нагрузки R11 выходного транзистора компаратора В, равен

0В и запрещает запуск процессора. Тем временем идет процесс подзаряда накопительных конденсаторов С4,

С5 и потенциал шины +5В растет. Поэтому протекает ток заряда конденсатора СЗ по цепи: шина +56 - R9 -

R8 - СЗ - "корпус".

Напряжение на конденсаторе СЗ, а значит, и на неинвертирующем входе компаратора В, растет.

Это возрастание происходит до тех пор, пока потенциал неинвертирующего входа компаратора В не начнет превышать

потенциал его инвертирующего входа. Как только это произойдет, компаратор В переключится, выходной транзистор

его закроется. Напряжение на шине +5В достигает к этому моменту номинального уровня. Поэтому сигнал PG

становится сигналом высокого уровня и разрешает запуск процессора. Таким образом, емкость конденсатора

СЗ обуславливает задержку при включении.

При выключении импульсного блока питания из сети исчезает переменное импульсное напряжение на вторичной обмотке

3-5 Т1. Поэтому конденсатор С1 малой емкости быстро разряжается, и напряжение на неинвертирующем входе

компаратора А быстро уменьшается до 0В. Напряжение на инвертирующем входе этого компаратора падает намного

медленнее за счет заряда на конденсаторе С2. Поэтому потенциал инвертирующего входа становится выше потенциала

неинвертирующего входа, и компаратор А переключается. Выходной транзистор его открывается. Поэтому потенциал

неинвертирующего входа компаратора В становится равен 0В. Потенциал инвертирующего входа компаратора В

еще положителен за счет заряда на конденсаторе С2. Поэтому компаратор В переключается, выходной транзистор

его открывается и сигнал PG становится сигналом низкого уровня, инициализируя сигнал системного сброса

RESET, прежде чем уменьшится ниже допустимого уровня питающее логические микросхемы напряжение +5 В.

Компараторы А и В охвачены положительными обратными связями с помощью резисторов R7 и R10

соответственно, что ускоряет их переключение.

Прецизионный резистивный делитель R5, R6 задает опорный уровень напряжения на инвертирующих

входах компараторов А и В в номинальном режиме работы.

Конденсатор С2 необходим для поддержания этого опорного уровня после выключения ИБП из сети.

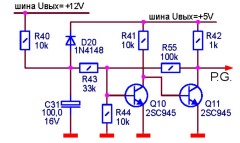

В заключение этого раздела приведем еще один вариант реализации схемы образования сигнала

PG (рис. 55).

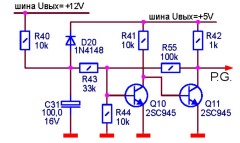

Рисунок 55. Схема образования сигнала PG в ИБП SP-200W.

Схема является однофункциональной, т.е. реализует только задержку появления разрешающего

сигнала PG при включении ИВП в сеть.

В этой схеме контролируемым сигналом является уровень напряжения на выходной шине канала

+12В. В основу построения схемы заложена схема двухкаскадного УПТ на транзисторах Q10, Q11, охваченная

положительной обратной связью с помощью резистора R55. Задержка опрокидывания этой схемы обусловлена наличием

конденсатора С31 сравнительно большой емкости в базовой цепи транзистора Q10 УПТ. После включения ИБП

в сеть, пока идет процесс выхода на режим, с выходной шины канала +12В протекает ток зарядки конденсатора

С31 по цепи: шина +12В -R40-C31 - "корпус".

Напряжение на конденсаторе С31 плавно возрастает. Пока это напряжение не достигает порогового

уровня опрокидывания схемы на транзисторах Q10, Q11, эта схема находится в состоянии, при котором транзистор

Q10 закрыт, а транзистор Q11 открыт током базы, который протекает с выходной шины канала +5В под воздействием

растущего напряжения на конденсаторах этой шины: шина +56 - R41 - 6-э Q11 - "корпус".

Поэтому сиигнал PG, снимаемый с коллектора Q11 равен 0В, и запрещает запуск процессора.

Тем временем растущее напряжение на конденсаторе С31 прикладывается к базовому делителю R43, R44 транзистора

Q10. К моменту достижения выходными напряжениями ИБП номинальных уровней напряжение на С31 достигнет уровня,

достаточного для возникновения лавинообразного процесса взаимного изменения состояний транзисторов Q10,

Q11 (благодаря наличию ПОС). В результате транзистор Q10 окажется открыт до насыщения, а транзистор Q11

закрыт. Поэтому сигнал PG станет сигналом высокого уровня и запуск процессора будет разрешен. Диод D20

служит для быстрой разрядки конденсатора С31 после выключения ИБП из сети. При этом С31 разряжается через

диод D20 и разрядный резистор выходной шины канала +5В ( на схеме не показан). Кроме того в процессе работы

ИБП этот диод ограничивает уровень напряжения на конденсаторе С31. Уровень ограничения составляет около

+5.8В.

Кроме вышеприведенных схем выработки сигнала PG могут применяться и другие принципы построения

схем, и задействоваться разное число компараторов микросхемы LM339N - от одного до четырех.

Адрес администрации сайта: admin@soundbarrel.ru

|