СХЕМЫ ЗАЩИТЫ

СТАТЬЯ ПОДГОТОВЛЕНА НА ОСНОВЕ КНИГИ А. В. ГОЛОВКОВА и В. Б ЛЮБИЦКОГО "БЛОКИ ПИТАНИЯ ДЛЯ СИСТЕМНЫХ МОДУЛЕЙ ТИПА IBM PC-XT/AT" ИЗДАТЕЛЬСТВА «ЛАД и Н»

СХЕМЫ ЗАЩИТЫ

Все защитные схемы, предусмотренные в схеме каждого конкретного ИБП, можно объединять под

общим названием "комбинированной защиты", т.к. срабатывание любой из этих защитных схем ведет

к отключению всех питающих напряжений от схемы компьютера посредством воздействия на управляющую микросхему

ИБП.

Все выходные каналы рассматриваемого класса ИБП можно условно, разделить на слабо- и сильноточные.

Условно сильноточными являются каналы положительных выходных напряжений +5В и +12В. Условно слаботочными

являются каналы отрицательных выходных напряжений -5В и -12В.

Проводя анализ работы разнообразных готовых защит, следует четко представлять себе их назначение,

которое заключается в ограничении потребляемого от сети тока. Это делается для того, чтобы предотвратить

выжигание чрезмерно большим током в первую очередь силовых транзисторов инвертора.

Данные схемы отличаются большим разнообразием. Тем не менее, несмотря на обилие конкретных

схемных решений, схемы защиты от КЗ можно классифицировать, во-первых, по функциональному назначению:

• защита от КЗ в нагрузке сильноточных каналов (+5В,+12В);

• защита от КЗ в нагрузке слаботочных каналов (-5В,-12В).

Необходимость раздельной организации защит для слаботочных и сильноточных каналов объясняется

тем, что чувствительность схемы защиты по сильноточным каналам недостаточна для случая КЗ в слаботочных

каналах.

Допустимая максимальная величина тока нагрузки в слаботочных каналах не превышает 1А. Превышение

этого порога означает возникновение аварийной ситуации.

Для сильноточных каналов суммарный ток нагрузки 15-20А не является аварийным. Поэтому при

токах нагрузки до 20-25А ( в зависимости от максимальной выходной мощности ИБП) токовая защита срабатывать

не должна. Это означает, что КЗ в слаботочном канале не будет классифицировано схемой управления как аварийный

режим из-за того, что порог срабатывания сильноточной защиты намного превышает величину тока КЗ в слаботочных

каналах. Другими словами, КЗ в слаботочных каналах не приведет к срабатыванию токовой защиты. Поэтому

схема защиты от КЗ в слаботочных каналах реализуется отдельно, как более чувствительная.

Необходимость организации защиты от КЗ в нагрузке слаботочных каналов, казалось бы, лишена

смысла. Действительно, ток КЗ слаботочных каналов относительно невелик, а значит, и ширина управляющих

импульсов на базах силовых транзисторов инвертора не будет в этом случае чрезмерно большой. Другими словами,

ИБП смог бы "выдержать" такой режим и продолжал бы работать без опасных последствий для силовых

транзисторов инвертора. Однако такой режим является ненормальным и опасен для самой нагрузки, так как

при КЗ в каком-либо из узлов компьютера невозможна нормальная его работа. Следовательно, при КЗ в нагрузке

слаботочных каналов необходимо производить защитное отключение всех выходных напряжений ИБП от схемы компьютера,

так же как и в случае КЗ в нагрузке сильноточных каналов.

Полный состав комбинированной защиты включает в себя:

• схему контроля ширины управляющего импульса;

• схему защитного отключения при КЗ в нагрузке слаботочных каналов;

• схему защиты от выходного перенапряжения.

Остановимся подробнее на механизмах защитного отключения и ограничения максимальной ширины

управляющего импульса. Оба эти механизма заложены в архитектуру ИМС TL494 и являются базовыми при конструировании

разных защитных схем. В классическом варианте построения комбинированной защиты возникновение КЗ в нагрузке

слаботочных каналов сразу же ведет к защитному отключению. При возникновении КЗ в нагрузке сильноточных

каналов сначала управляющая микросхема переходит в режим ограничения, и если КЗ продолжает развиваться,

то происходит защитное отключение.

Суть и смысл защитного отключения заключаются в том, чтобы силовые транзисторы инвертора

переставали переключаться и оставались бы в закрытом состоянии неограниченно долго при возникновении аварийной

ситуации, называемой коротким замыканием в нагрузке любого из выходных каналов ИБП. Для того чтобы оба

силовых транзистора инвертора оказались закрыты одновременно, на их базах не должно быть управляющих импульсов.

Тогда первичная обмотка силового импульсного трансформатора окажется отключенной от шины выпрямленного

напряжения сети и, следовательно, через первичную обмотку и силовые транзисторы не будет протекать ток.

Поэтому силовые транзисторы не будут подвержены опасности выжигания этим чрезмерно большим током при КЗ

на вторичной стороне. Таким образом при исчезновении управляющих импульсов на базах силовых транзисторов

желаемый защитный эффект будет достигнут.

Источником (генератором) управляющих импульсов является микросхема TL494. Поэтому для осуществления

защитного отключения необходимо заблокировать ее работу. Это можно сделать, если принудительно заставить

любой из компараторов DA1, DA2 прекратить переключения и перейти в статическое состояние с постоянным

высоким уровнем напряжения (логическая 1) на выходе. Тогда работа всего цифрового тракта микросхемы будет

заблокирована. Оба выходных транзистора ее окажутся в статическом закрытом состоянии и управляющие импульсы

на выводах 8 и 11 (либо 9 и 10) исчезнут, превратившись в статические потенциалы, которые не могут передаться

на базы силовых транзисторов, т.к. связь с ними осуществляется через управляющий трансформатор DT. Для

того чтобы прекратить переключения компаратора DA1 либо DA2, достаточно на его неинвертирующий вход (вывод

4 для компаратора, DA1 либо вывод 3 для компаратора DA2) подать статический потенциал, превышающий амплитуду

пилообразного напряжения, поступающего на инвертирующие входы обоих компараторов (вывод 5) с выхода генератора

пилообразного напряжения DA6. Амплитуда пилообразного напряжения, как отмечалось ранее, составляет +3.2В.

Поэтому, если построить схему защиты так, что на вывод 4 либо на вывод 3 ИМС TL494 в результате короткого

замыкания в нагрузке будет подан статический потенциал, превышающий +3.2В, то произойдет блокировка работы

ИМС. Однако необходимо отметить, что генератор пилообразного напряжения при этом не прекращает своей работы,

т.е., несмотря на отсутствие выходных импульсов, пилообразное напряжение продолжает вырабатываться.

Этот базовый принцип и положен в основу построения всех вариантов схем защитного отключения,

применяемых в разных схемах ИБП на основе управляющей микросхемы TL494. При этом необходимо понимать,

что термин "защитное отключение" подразумевает отключение (закрывание) именно силовых транзисторов

инвертора, а не управляющей микросхемы, которая продолжает работать в специфическом режиме блокировки

ее цифрового тракта до тех пор, пока на шине питания микросхемы Upom имеется напряжение, превышающее уровень+7В.

Датчиком для типовой схемы защитного отключения обычно является диодно-резистивньй либо

резистивный делитель, подключаемый к шинам выходных напряжений ИБП. Такой делитель "контролирует"

уровень напряжения на этих шинах. При КЗ в нагрузке какой-либо из контролируемых шин изменяется распределение

потенциалов в узлах такого делителя-датчика, что и является сигналом на срабатывание для схемы защитного

отключения.

Механизм ограничения максимальной длительности управляющего импульса имеет другую структуру.

Из функциональной схемы микросхемы TL494 (рис.12) видно, что напряжение на неинвертирующем входе ШИМ-компаратора

DA2 определяется наибольшим из выходных напряжений двух усилителей ошибки DA3, DA4.

Для того чтобы выходные напряжения усилителей DA3, DA4 не влияли бы друг на друга, выходы

этих усилителей подключены к неинвертирующему входу ШИМ-компаратора DA2 через развязывающие диоды, расположенные

внутри микросхемы.

Основная идея, заложенная в построение механизма ограничения, состоит в том, что усилитель

DA4 включается так; чтобы изменение его выходного напряжения при растущей ширине управляющих импульсов,

было бы противоположным изменению выходного напряжения усилителя DA3.

Рассмотрим динамику процесса ограничения.

Пусть в нагрузке какого-либо из сильноточных каналов ИБП возник режим повышенного токопот-ребления

(начальная стадия КЗ). Выходное напряжение в канале +5В уменьшается. Это уменьшение через цепь обратной

связи передается на неинвертирующий вход усилителя ошибки DA3 (вывод 1 микросхемы). Выходное напряжение

DA3, а значит, и напряжение на неинвертирующем входе ШИМ-компараторе DA2 начинает уменьшаться. Благодаря

этому ширина выходных управляющих импульсов микросхемы возрастает, т.е. управляющая микросхема стремится

поддержать выходные напряжения ИБП на прежнем уровне за счет увеличения времени открытого состояния силовых

транзисторов. На один из входов усилителя ошибки DA4 подается сигнал обратной связи, уровень которого

пропорционален ширине управляющих импульсов ( времени открытого состояния силовых транзисторов). Уровень

этого сигнала в рассматриваемой ситуации будет возрастать. При этом DA4 включается так, что выходное напряжение

его с ростом уровня сигнала обратной связи также растет. В результате имеют место два противоположно направленных

процесса. Выходное напряжение усилителя ошибки DA3 уменьшается (как результат уменьшения выходных напряжений

ИБП), а выходное напряжение усилителя ошибки DA4 растет (как результат увеличения ширины управляющих импульсов).

Пока выходное напряжение усилителя DA3 превышает выходное напряжение усилителя DA4, оно является превалирующим

и определяет уровень напряжения на неинвертирующем входе ШИМ-компаратора DA2, а значит, и ширину выходных

импульсов, которая растет со скоростью, равной скорости уменьшения выходного напряжения усилителя DA3.

Однако наступает момент, когда убывающее выходное напряжение усилителя DA3 сравнивается

с растущим выходным напряжением усилителя DA4. После этого выходное напряжение усилителя DA3 становится

меньше, чем выходное напряжение усилителя DA4 и перестает влиять на ширину выходных импульсов микросхемы.

Другими словами, в этот момент происходит "передача" управляющих функций от усилителя DA3 к

усилителю DA4. Ширина выходных импульсов определяется теперь только выходным напряжением усилителя DA4,

которое не зависит от уровня выходных напряжений ИБП и сигнала обратной связи на выводе 1 микросхемы.

Поэтому увеличение ширины выходных импульсов прекращается.

Параметры элементов схемы рассчитываются таким образом, чтобы ограничение происходило на

безопасном для транзисторов инвертора уровне. При этом скорость, с которой система переходит в режим ограничения,

а также уровень этого ограничения, зависят от наличия и глубины обратных связей, которые могут организовываться

с помощью внешних RC-цепочек в различной комбинации, охватывающих усилитель ошибки DA4.

Далее микросхема переходит в специфический режим работы называемый режимом ограничения.

Этот режим характеризуется тем, что ширина управляющих импульсов на выходах микросхемы неизменна и не

зависит от уровня выходных напряжений ИБП.

Другими словами, механизм ШИМ в режиме ограничения отключается (не действует).

Если КЗ в нагрузке самоустранилось по истечении некоторого времени, то накопительные конденсаторы

вторичной стороны быстро заряжаются. Поэтому сигнал обратной связи, поступающий на неинвертирующий вход

усилителя DA3, начинает возрастать. Следовательно, начинает возрастать и выходное напряжение DA3. Когда

это напряжение достигнет уровня выходного напряжения усилителя DA4, то вновь произойдет передача управления

и управляющие функции перейдут от усилителя DA4 к усилителю DA3.

Если КЗ в нагрузке не самоустранилось, то поскольку имеет место режим ограничения, микросхема

не в состоянии поддерживать напряжения на выходных шинах ИБП. Поэтому выходные напряжения ИБП быстро уменьшаются,

что приводит в большинстве практических схем ИБП к срабатыванию механизма защитного отключения.

Защитное отключение, как было показано выше, имеет своим результатом прекращение протекания

тока через силовые транзисторы и первичную обмотку импульсного трансформатора. Поэтому сигнал от токового

датчика, поступающий на усилитель ошибки DA4, становится равным 0. Схема ИБП приходит в исходное состояние.

Поэтому срабатывает схема пуска и ИБП попытается вновь выйти в номинальный режим. Если за это время КЗ

в нагрузке самоустранилось, то выход на режим ничем не будет отличаться от первоначального запуска при

включении ИБП в сеть. Если же КЗ не самоустранилось, то процессы повторятся, и ИБП перейдет в специфический

аварийный "икающий" режим, который представляет собой периодически повторяющийся процесс защитного

отключения.

В качестве датчика ширины управляющих импульсов могут использоваться разные элементы. Информацию

о ширине управляющих импульсов можно получить как с первичной, так и со вторичной стороны ИБП. Поэтому

традиционными являются два основных способа, которые позволяют получить желаемый эффект контроля при минимальных

затратах и простоте схемотехнической реализации.

Первый из этих способов заключается в том, что управляющие импульсы снимаются либо со средней

точки первичной обмотки управляющего трансформатора (DT), либо со специальной дополнительной обмотки этого

трансформатора, которые находятся на вторичной стороне ИБП. Далее из этой импульсной последовательности

выделяется постоянная составляющая. Уровень этой составляющей и несет в себе информацию о ширине управляющих

импульсов.

Способ получения информации о ширине управляющих импульсов с первичной стороны ИБП заключается

в том, что в цепь протекания тока первичной обмотки силового импульсного трансформатора последовательно

включается первичная (токовая) обмотка трансформатора тока. Применение а качестве датчика такого элемента

как трансформатор объясняется необходимостью гальванической развязки вторичной стороны ИБП от первичной.

Ток через первичную обмотку силового импульсного трансформатора имеет импульсную форму,

причем ширина токовых импульсов определяется временем открытого состояния силовых транзисторов инвертора,

т.е. шириной управляющих импульсов на базах этих транзисторов. Поэтому напряжение на нагрузке вторичной

обмотки трансформатора тока также будет импульсным, причем длительность этих импульсов будет равна длительности

управляющих импульсов, вырабатываемых микросхемой. Далее, как и в первом случае, из этого импульсного

напряжения выделяется постоянная составляющая (посредством выпрямления и фильтрации). Уровень постоянной

составляющей несет в себе информацию о ширине управляющих импульсов.

Контролируемый сигнал, уровень которого зависит от ширины управляющих импульсов, подается

на один из двух входов усилителя ошибки DA4. На второй вход этого усилителя для сравнения подается эталонное

напряжение, уровень которого выбирается для каждой конкретной схемы ИБП исходя из построения всей защитной

схемы в целом. Этот уровень лежит в диапазоне от 0 (в этом случае опорный вход усилителя DA4 заземлен)

до +5В (в этом случае на опорный вход усилителя DA4 подается напряжение Uref. Если опорный уровень выбирается

внутри этого диапазона, то к шине Uref подключается резистивный делитель и опорное напряжение необходимого

уровня снимается с него. В качестве опорного входа обычно выбирается неинвертируюший вход усилителя DA4

(вывод 16 микросхемы), а контролируемый сигнал подается на инвертирующий вход (вывод 15). Однако возможен

и обратный вариант включения усилителя DA4. При этом основным правилом, которое необходимо соблюсти при

построении схемы ограничения, является то, что с ростом ширины управляющих импульсов выходное напряжение

усилителя DA4 должно расти.

Практические схемы ИБП на основе управляющей микросхемы TL494 могут быть построены как с

использованием обоих защитных механизмов, так и с использованием только одного из них. В схемах, использующих

оба механизма, при повышенном токопотреблении в нагрузке сильноточных каналов сначала имеет место режим

ограничения ширины управляющих импульсов, и лишь только затем, если КЗ продолжает развиваться, наступает

защитное отключение.

В схемах с использованием только механизма защитного отключения чрезмерная ширина управляющих

импульсов сразу вызывает защитное отключение. Сигнал с датчика ширины управляющих импульсов в этих схемах

подается на неинвертирующий вход какого-либо из компараторов DA1, DA2. Т.к. механизм ограничения в этих

схемах не используется, то усилитель ошибки DA4 становится не нужен. Поэтому его принудительно выставляют

в состояние жесткого нуля по выходу с тем, чтобы его выходное напряжение не влияло бы на входное напряжение

ШИМ-компа-ратора DA2 ни при каких условиях. Для этого на инвертирующий вход DA4 (вывод 15) сразу при включении

ИВП подается опорное напряжение Uref с вывода 14, а неинвертирующий вход (вывод 16) заземляется.

Отказ от использования механизма ограничения при построении комбинированной защиты принципиально

возможен, т.к. в архитектуре самой управляющей микросхемы уже заложено ограничение максимальной ширины

выходного импульса. Уровень этого ограничения определяется потенциалом на выводе 4 микросхемы в установившемся

режиме, а также источником напряжения DA7 (0,1В), подключенным между выводом 4 и неинвертирующим входом

компаратора DA1(см. выше). Таким образом внешняя схема ограничения (если она имеется) дублирует внутреннюю

схему, повышая надежность работы ИБП и уменьшая вероятность выхода из строя силовых транзисторов инвертора.

Отдельно необходимо упомянуть о защите от выходного перенапряжения. Поскольку самым "страшным"

по возможным последствиям является перенапряжение в канале выходного напряжения +5В, которым питаются

логические интегральные схемы, то защита организуется, как правило, именно в этом канале. В схемах некоторых

ИБП предусмотрена и защита от перенапряжения в канале +12В. Перенапряжение в слаботочных каналах выработки

отрицательных напряжений не столь критично для работы компьютера. Поэтому в этих каналах такой защиты,

как правило, нет. Датчиком схемы защиты от выходного перенапряжения обычно является пороговая схема, состоящая

из стабилитрона с соответствующим пробивным напряжением и балластного резистора. Стабилитрон подключается

к шине контролируемого напряжения. При превышении этим напряжением заданного расчетного уровня стабилитрон

пробивается, и на балластном резисторе появляется потенциал как результат протекания по нему тока стабилитрона.

Появление этого потенциала используется как сигнал на срабатывание для схемы защитного отключения.

Подводя итог описанию отдельных компонентов, входящих в состав комбинированной защиты, необходимо

отметить, что наличие всех перечисленных защитных схем не является обязательным. Некоторые из них могут

отсутствовать.

Приведем условную классификацию компонентов комбинированной защиты.

Схемы контроля ширины управляющих импульсов можно разделить на:

• схемы, использующие механизм ограничения (ограничивающие схемы контроля);

• схемы, использующие механизм защитного отключения (отключающие схемы контроля).

Схемы защиты от короткого замыкания в нагрузке можно разделить на:

• полные, в которых контроль осуществляется за уровнями всех четырех выходных напряжений;

• неполные, в которых контроль осуществляется только за уровнями отрицательных выходных

напряжений -5В и -12В.

Схемы контроля выходного перенапряжения также можно разделить на:

• полные, контролирующие уровень напряжений на шинах +5В и +12В;

• неполные, контролирующие уровень напряжения только на одной из этих шин.

Рассмотрим конкретные примеры.

Пример 1.

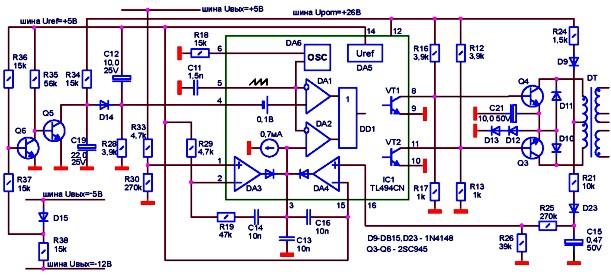

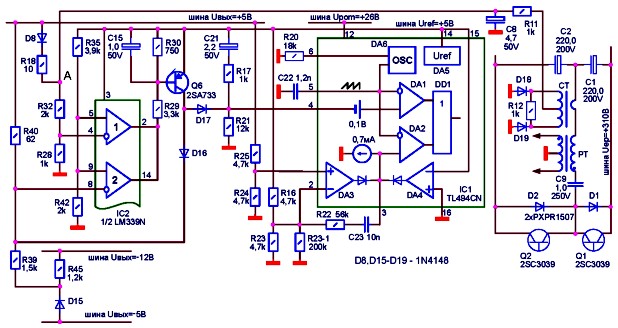

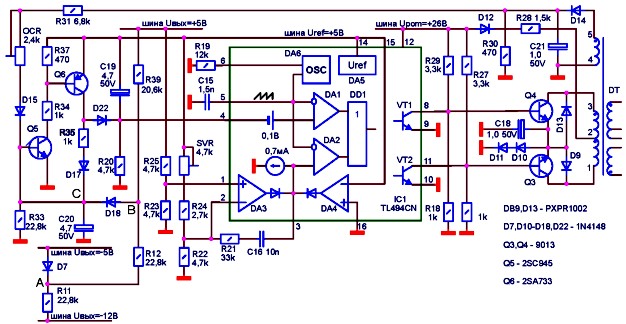

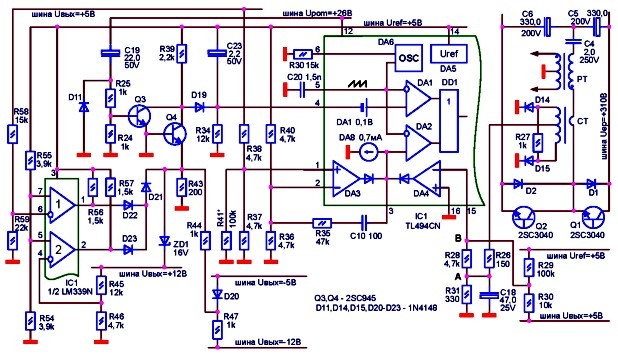

Комбинированная защита ИБП GT-150W (рис. 40) включает в себя:

• ограничивающую схему контроля ширины управляющих импульсов;

• неполную схему защиты от КЗ в нагрузке.

Рисунок 40. Комбинированная защита ИБП GT-150W

Схема контроля ширины управляющих импульсов работает следующим образом. На инвертирующий

вход усилителя ошибки DA4 (вывод 15) подается опорное напряжение Uref с вывода 14. На неинвертирующий

вход (вывод 16) подается контролируемый потенциал, уровень которого пропорционален ширине управляющих

импульсов. Потенциал этот получается путем выпрямления импульсного напряжения, возникающего при работе

ИБП в средней точке первичной обмотки управляющего трансформатора DT. Это импульсное напряжение выпрямляется

диодом D23, и сглаживается конденсатором С15. Резистор R21 гасит амплитуду этого импульсного напряжения

до необходимого уровня. Напряжение с конденсатора С15 подается на резистивный делитель R25, R26, с резистора

R26 которого часть этого напряжения подается на неинвертирующий вход усилителя DA4. Конденсаторы CIS,

C16 образуют цепь коррекции АЧХ усилителя DA4.

В режиме нормального токопотребления, когда ширина управляющих импульсов не выходит за пределы

диапазона стабилизации, потенциал вывода 15 микросхемы IC1 всегда больше потенциала вывода 16. Поэтому

выходное напряжение усилителя ошибки DA4 равно 0В и не влияет на работу микросхемы. При возрастании ширины

управляющих импульсов в результате повышенного токопотребления в нагрузке какого-либо из сильноточных

каналов, потенциал на конденсаторе С15, а следовательно, и на выводе 16 управляющей микросхемы начинает

расти. Когда он достигает опорного уровня Uref=+5B на выводе 15 выходное напряжение усилителя DA4 начинает

возрастать. Если КЗ в нагрузке продолжает развиваться, требуя все большей ширины управляющего импульса

для поддержания выходных напряжений ИБП, то выходное напряжение усилителя DA4 быстро возрастает наряду

с уменьшением выходного напряжения усилителя DA3, которое определяется уровнем сигнала обратной связи.

Этот сигнал снимается с резистора R30 делителя R33, R30, подключенного к шине выходного напряжения +5В.

В момент, когда выходные напряжения обоих усилителей сравниваются, управление ШИМ-компаратором DA2 передается

от усилителя DA3 к усилителю DA4 и становится независимым от уровня сигнала обратной связи на выводе 1

управляющей микросхемы. Поэтому увеличение ширины управляющих импульсов прекращается и микросхема переходит

в режим ограничения. Если КЗ продолжает развиваться, то вступает в действие механизм защитного отключения,

т.к. все выходные напряжения ИБП (в том числе и в слаботочных каналах) уменьшаются, стремясь к уровню

0В.

Неполная схема защитного отключения при КЗ в нагрузке слаботочных каналов выполнена традиционным

способом. Между шинами выходных напряжений -5В и -12В включен делитель-датчик D15, R38. К средней точке

делителя подключен резистор R37, входящий в базовый для транзистора Q6 делитель R36, R37. Транзистор Q6

вместе с транзистором Q5 образуют двухкаскадный УПТ. Резистор R35 - коллекторная нагрузка первого каскада

УПТ и одновременно R35 и сопротивление участка коллектор-эмиттер транзистора Q6 образуют базовый делитель

для второго транзистора УПТ Q5. Коллекторной нагрузкой транзистора Q5 является резистор R34, сигнал с

которого снимается на вход защитного отключения 4 управляющей микросхемы через диод D14.

В нормальном режиме работы потенциал средней точки делителя-датчика D15, R38 составляет

около -5,8В, т.к. потенциал этой точки ниже потенциала шины -5В на величину прямого падения напряжения

на диоде D15, благодаря протеканию через делитель тока по цепи: шина -5В - D15 -R38- шина-12В.

Поэтому базовый делитель транзистора. Q6 -R36, R37 запитан двуполярно: напряжением Uref,

с одной стороны, и напряжением -5,8В, с другой. Номиналы резисторов делителя R36, R37 - одинаковы (15кОм).

Поэтому потенциал базы транзистора Q6 в нормальном режиме работы будет отрицательным (около -0,4В). Поэтому

Q6 будет закрыт, а транзистор Q5, наоборот, открыт током базы, протекающим по цепи: шина Uref - R35 -6-3Q5-

"корпус".

Напряжение на конденсаторе С 19 поэтому будет равно 0В, и потенциал вывода 4 управляющей

микросхемы после завершения процесса плавного запуска (см. ниже) также будет равен 0В.

При КЗ в нагрузке канала -12В диод D15 делителя-датчика закроется, т.к. потенциал шины -12В

в режиме КЗ равен 0В, и на катоде D15 появится положительный потенциал с резистора R38, через который

протекает ток по цепи: шина Uref -R36 - R37 - R38 - "корпус".

Следовательно, потенциал базы транзистора Q6 увеличится и станет положительным. Поэтому

Q6 откроется до насыщения, и потенциал базы транзистора Q5 станет равен 0В. Это приведет к запиранию транзистора

Q5 и увеличению потенциала его коллектора. Уровень коллекторного потенциала Q6 определяется номиналами

резисторов делителя R34, D14, R28, который подключен к шине вспомогательного напряжения питания микросхемы

Upom=+26B. Произведя несложный расчет, можно убедиться, что при закрытом состоянии транзистора Q6 потенциал

его коллектора составляет около +6В. Эта величина, подаваемая на неинвертирующий вход компаратора DA1

через диод развязки D14, составит около +5В, что превышает амплитуду пилообразного напряжения на инвертирующем

входе DA1. Поэтому DA1 перестает переключаться, и работа цифрового тракта микросхемы блокируется. Управляющие

импульсы на выходах 8, 11 исчезают, а силовые транзисторы инвертора (на схеме не показаны) перестают переключаться.

Первичная обмотка импульсного трансформатора оказывается отключена от шины Uep, и токопотребление от сети

прекращается.

При КЗ в нагрузке канала -5В потенциал средней точки делителя-датчика D15, R38 составит

всего -0,8В, что также приведет к закрыванию транзистора Q6, открыванию транзистора Q5 и защитному отключению.

Схема контроля выходного перенапряжения в данном ИБП отсутствует.

Элементы С12, R28 образуют формирующую щепочку схемы плавного запуска. Диод D14 служит для

развязки формирующей цепочки от выходного напряжения УПТ.

Для полноты информации отметим, что в данной схеме оригинальным является подбор делителей,

задающих уровни сигналов на входах усилителя ошибки DA3. На инвертирующий вход 2 в качестве опорного подается

полное напряжение Uref с вывода 14. Уровень на неинвертирующем входе 1 подбирается с помощью высокоомного

R30, который включается последовательно с R33 и образует с ним делитель, благодаря чему уровень потенциала

на неинвертирующем входе DA3 получается чуть ниже, чем потенциал шины выходного напряжения +5В. Этим и

создается начальная разность между опорным и отслеживаемым уровнями (ошибка), которая определяет выходное

напряжение DA3.

Транзисторы Q4, Q3 совместно с управляющим трансформатором DT образуют согласующий каскад,

выполненный по транзисторной схеме с общим управлением. Питание на каскад подается традиционным способом

с шины Upom. Коллекторными нагрузками транзисторов Q4, Q3 являются полуобмотки первичной обмотки DT и

резистор общей нагрузки R24. Диод D9 - развязывающий.

Очевидно, что импульсное напряжение в средней точке первичной обмотке DT получается в результате

того, что коллекторная нагрузка, транзисторов Q3, Q4 выполнена как разделенная. Другими словами, если

бы резистор R24 отсутствовал, то напряжение в средней точке первичной обмотки DT было бы равно Upom (за

вычетом прямого падения напряжения на диоде D9), и поэтому не могло бы служить источником информации о

ширине управляющих импульсов, вырабатываемых микросхемой.

Пример 2.

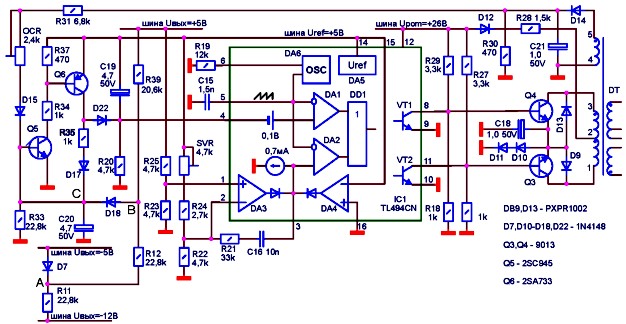

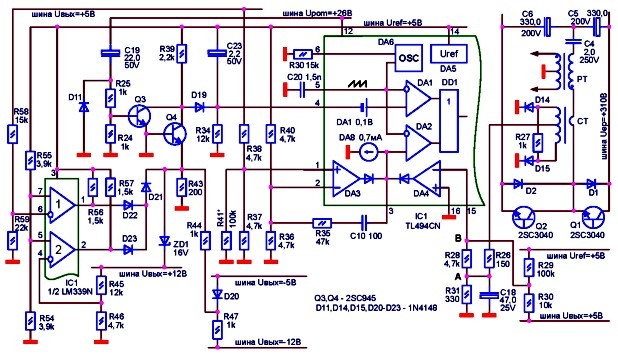

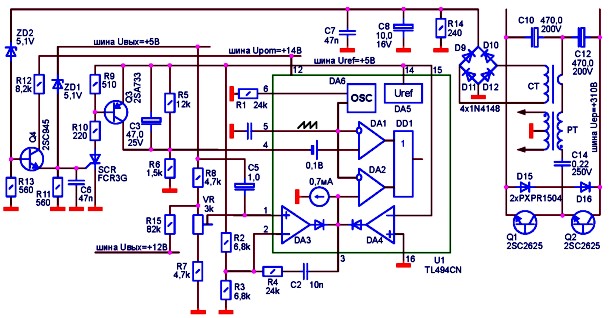

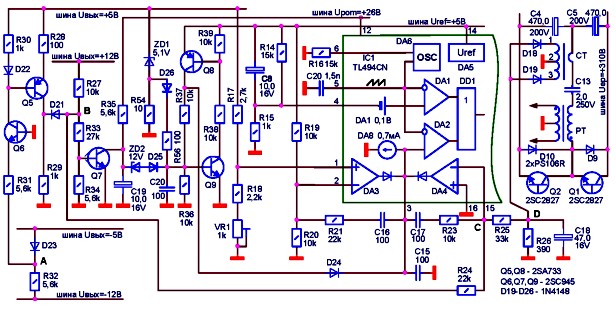

Комбинированная защита ИБП LPS-02-150XT (рис. 41) включает в себя:

• отключающую схему контроля цгарины управляющих импульсов;

• неполную схему защиты от КЗ в нагрузке;

• неполную схему контроля выходного перенапряжения.

Рисунок 41. Комбинированная защита ИБП LPS-02-150XT

Отключающая схема контроля ширины управляющих импульсов выполнена оригинальным способом.

Датчиком импульсного напряжения является специальная дополнительная обмотка 4-5 управляющего трансформатора

DT. Импульсное знакопеременное напряжение, возникающее на отводе 5 этой обмотки при работе ИБП, выпрямляется

диодом D14 и сглаживается конденсатором С21. Резистор R30 выполняет функцию нагрузки выпрямителя. Напряжение

с конденсатора С21 подается на диодно-резистивный делитель R31, OCR, D15, R33. Однако потенциал на резисторе

R33 определяется не только напряжением на конденсаторе С21. Этот потенциал (в точке С) определяется также

уровнями напряжений на выходных шинах +5, -5, -12 В, которые связаны между собой диодно-резистивным делителем

R39, R12, D7, R11. Потенциал точки В этого делителя через диод развязки D18 подается на резистор R33.

Потенциал точки С определяет потенциал базы транзистора Q5 бистабильнои схемы, собранной на транзисторах

Q5, Q6. Биста-бильная схема, в свою очередь, определяет потенциал входа защитного отключения 4 управляющей

микросхемы. Несложный расчет позволяет установить, что в нормальном режиме работы, когда все выходные

напряжения ИБП имеют номинальный уровень, потенциал точки С будет близок к 0В, поэтому оба транзистора

бистабильнои схемы закрыты, а потенциал вывода 4 управляющей микросхемы равен 0В.

В случае повышенного токопотребления в нагрузке сильноточных каналов ширина управляющих

импульсов, генерируемых микросхемой, а значит и импульсов на отводе 5 обмотки 4-5 DT, увеличивается. Поэтому

увеличивается уровень выпрямленного напряжения на конденсаторе С21, и, в конечном итоге, на базе транзистора

Q5, который приоткрывается, что вызывает протекание базового тока транзистора Q6. Так как бистабиль-ная

схема охвачена положительной обратной связью с помощью цепочки R35, D17, то появление коллекторного тока

Q6 приводит к лавинообразному процессу взаимного отпирания обоих транзисторов. Поэтому напряжение Uref,

которым запитан по эмиттеру транзистор Q6 бистабильнои схемы, оказывается приложенным через его малое

внутреннее сопротивление и диод развязки D22 к выводу 4 управляющей микросхемы. Это, как было показано

выше, приводит к защитному отключению.

Резистор OCR выполнен как подстроечный. Это позволяет при настройке ИБП выбрать тот уровень

напряжения на конденсаторе С21 (другими словами, ту максимальную ширину управляющих импульсов), при превышении

которого будет происходить защитное отключение.

Элементы С19, R20 образуют формирующую цепочку схемы плавного запуска. Диод D22 развязывает

формирующую цепочку от бистабильнои схемы.

Уровни выходных напряжений ИБП устанавливаются при настройке с помощью переменного резистора

SVR, определяющего уровень опорного напряжения на инвертирующем входе усилителя ошибки DA3.

Механизм ограничения ширины управляющего импульса здесь не используется. Поэтому усилитель

ошибки DA4 исключается из работы микросхемы. Для этого на его инвертирующий вход (вывод 15) подается напряжение

Uref, а неинвертирующий вход (вывод 16) заземляется.

При КЗ в нагрузке любого из слаботочных каналов потенциалы точек А, В, С возрастают. Это

приводит к открыванию обоих транзисторов бистабильнои схемы, и защитному отключению. Аналогичный эффект

вызовет перенапряжение в канале +5В. Увеличение напряжения на шине +5В передастся через диод D18 на базу

транзистора Q5 (в точку С). Это вызовет открывание транзисторов бистабильнои схемы и защитное отключение.

Пример З.

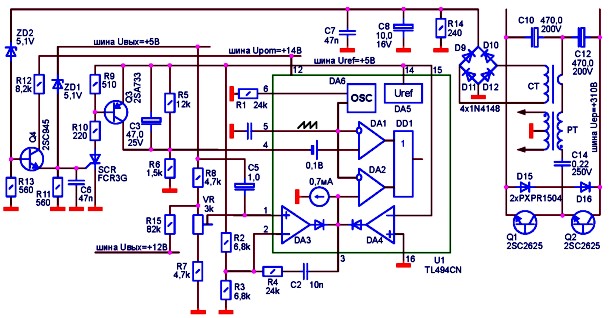

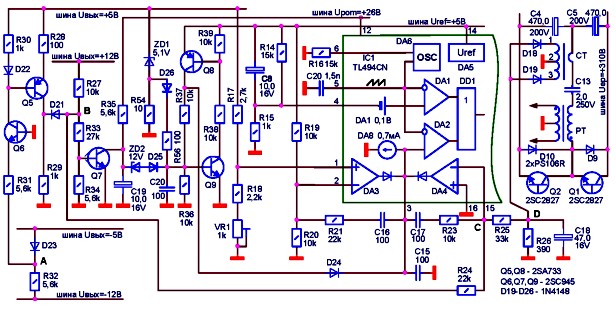

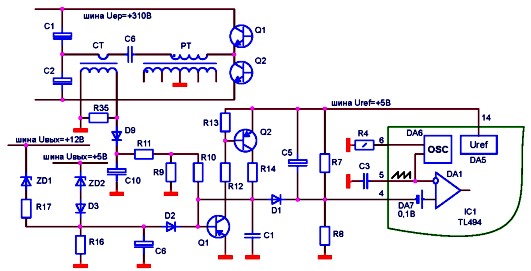

Комбинированная защита ИБП PS-200B (рис. 42) включает в себя:

• отключающую схему контроля ширины управляющего импульса;

• неполную схему контроля перенапряжения.

Рисунок 42. Комбинированная защита ИБП PS-200B

Отключающая схема контроля ширины управляющего импульса имеет датчик, расположенный на

первичной стороне ИБП (в отличие от предыдущих двух случаев). Этим датчиком является трансформатор тока

СТ, первичная обмотка которого включена последовательно с первичной обмоткой силового импульсного трансформатора

РТ. Токовые импульсы, протекающие по первичной обмотке СТ, трансформируются во вторичную его обмотку,

выпрямляются с помощью мостовой схемы D9-D12 и сглаживаются конденсатором С8. Резистор R14 является нагрузкой

вторичной обмотки СТ. Наличие этой нагрузки является обязательным условием нормальной работы СТ. Уровень

напряжения на конденсаторе С8 пропорционален ширине токовых импульсов через первичную обмотку СТ (а значит,

и ширине управляющих импульсов на базах силовых транзисторов Q1, Q2 инвертора). Это напряжение подается

на пороговую схему, собранную на стабилитроне ZD2 и резисторе R13. Пробивное напряжение стабилитрона ZD2

равно 5,1В.

В режиме нормального токопотребления, когда ширина управляющих импульсов не превышает допустимую

величину, напряжение на конденсаторе С8 не превышает уровень +5,1В. Поэтому стабилитрон ZD2 закрыт и потенциал

базы транзистора, Q4 равен 0В. Транзистор Q4 закрыт, а поэтому закрыты тиристор SCR и транзистор Q3 бистабильной

схемы. Поэтому потенциал вывода 4 управляющей микросхемы определяется номиналами резисторов делителя R5,

R6, подключенного к шине Uref. Из схемы видно, что при закрытом транзисторе Q3 потенциал вывода 4 в установившемся

режиме составит 0,55В. Переключения компаратора DA1 поэтому не влияют на работу микросхемы. При повышенном

токопотребле-нии в нагрузке какого-либо из сильноточных каналов ширина управляющих импульсов возрастает.

Поэтому напряжение на конденсаторе С8 повышается. Когда это напряжение превысит уровень +5,1В, стабилитрон

ZD2 "пробивается", и в базу транзистора Q4 течет открывающий его ток по цепи: (+)С8 - ZD2 -

б-э Q4 - R11 - "корпус".

Транзистор Q4 открывается, и в управляющий электрод тиристора SCR течет открывающий его

ток по цепи: шина Upom - R12 - к-э Q4 - управляющий переход SCR - "корпус".

Тиристор открывается и подключает резистор R10 базового делителя R9, R1Q транзистора Q3

к "корпусу". Это вызывает открывание транзистора Q3 базовым током, протекающем по цепи: шина

Uref- 9-6Q3- R10-a-KSCR - "корпус".

Транзистор Q3 запитан по эмиттеру напряжением Uref с вывода 14 микросхемы. Поэтому при открывании

Q3 это напряжение оказывается приложенным через его малое внутреннее сопротивление к выводу 4 управляющей

микросхемы, что вызывает защитное отключение.

Схема защиты от КЗ в нагрузке слаботочных каналов в данном ИБП отсутствует.

Схема защиты от выходного перенапряжения в канале +5В собрана на элементах ZD1, R11. При

превышении напряжением на шине +5В пробивного напряжения стабилитрона ZD1 (5,1В), он "пробивается",

и в управляющий электрод тиристора SCR течет ток, открывающий его. Это приводит к открыванию транзистора

Q3 и защитному отключению.

Механизм ограничения ширины управляющих импульсов здесь не используется. Поэтому традиционно

на инвертирующий вход усилителя ошибки DA4 (вывод 15) подается напряжение Uref, a неинвертирующий вход

(вывод 16) заземляется.

Особо необходимо отметить, что в схеме данного ИБП не используется метод групповой стабилизации

выходных напряжений, т.е. дроссель групповой стабилизации на выходе ИБП отсутствует. Стабилизация производится

только по двум каналам: +5В и +12В гальваническим способом. Между шинами выходных напряжений +5В и +12В

включен резистивный делитель-датчик R15, R8. Потенциал в средней точке этого делителя является контролируемым

сигналом и подается на резистивный делитель, состоящий из переменного резистора VR и резистора R7. Поэтому

сигнал обратной связи, поступающий на неинвертирующий вход усилителя ошибки DA3, является суммарным, т.к.

изменение уровня напряжения на любой из шин +5В, +12В отразится на величине потенциала в средней точке

делителя-датчика R15, R8, а значит, и на величине сигнала обратной связи, снимаемого с движка переменного

резистора VR на неинвертирующий вход усилителя ошибки DA3.

Пример 4.

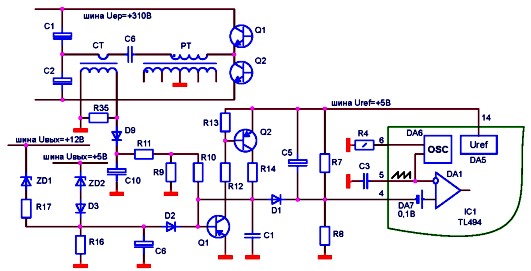

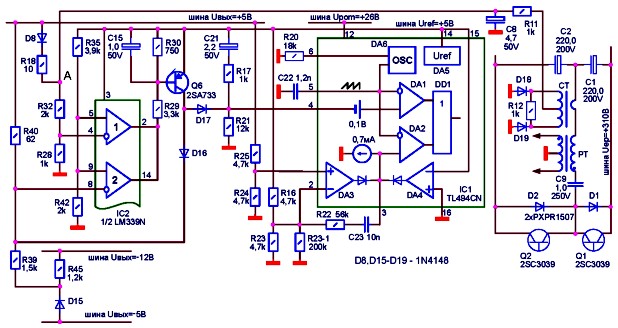

Комбинированная защита ИБП ESP-1003R (рис. 43) включает в себя:

• отключающую схему контроля ширины управляющего импульса;

• полную схему контроля перенапряжения на выходных шинах сильноточных каналов.

Рисунок 43. Комбинированная защита ИБП ESP-1003R (ESAN ELECTRONIC COMPANY, Ltd.)

Эта схема похожа на схему рис.41. Принцип действия отключающей схемы контроля ширины управляющего

импульса тот же, что и ранее, за исключением того, что информация о ширине управляющего импульса получается

с первичной стороны ИБП. В качестве датчика традиционно используется трансформатор тока СТ, первичная

обмотка которого включена последовательно с первичной обмоткой силового импульсного трансформатора РТ.

При протекании через первичную обмотку СТ пилообразных импульсов тока на нагрузке его вторичной обмотки

(резистор R35) выделяется знакопеременное прямоугольное импульсное напряжение. Это напряжение выпрямляется

однополупериодным выпрямителем D9 и сглаживается конденсатором СЮ. Уровень напряжения на конденсаторе

C1Q пропорционален ширине токовых импульсов через первичную обмотку СТ, а значит и ширине управляющих

импульсов на базах силовых транзисторов инвертора. Напряжение с конденсатора СЮ подается на рези-стивный

делитель R11, R9. Часть этого напряжения снимается с резистора R9 делителя и через резистор R10 подается

на базу транзистора Q1, который вместе с транзистором Q2 образует бис-табильную схему, определяющую уровень

потенциала на выводе 4 управляющей микросхемы IC1.

Пока ширина управляющих импульсов не выходит за расчетный предел, напряжение на конденсаторе

СЮ близко к 0В, и поэтому оба транзистора Q1, Q2 будут закрыты. При возрастании ширины управляющего импульса,

например в результате повышенного токопотребления в нагрузке какого-либо из сильноточных каналов, уровень

постоянного напряжения на конденсаторе СЮ возрастает. Это приводит к приоткрывайию транзистора Q1 базовым

током, протекающим по цепи: (+)С10 -R11 - R10 - 6-э Q1 - "корпус"- (-)СЮ.

Приоткрывание транзистора Q1 влечет за собой приоткрывание транзистора Q2 базовым током,

протекающим по цепи: шина Uref - э-б Q2 -R12 - к-э Q1 - "корпус".

Приоткрывание транзистора Q2 приводит к еще большему приоткрыванию транзистора Q1, т.к.

коллектор транзистора Q2 подключен через резистор R14 к базе транзистора Q1, т.е. между транзисторами

имеется положительная обратная связь. Лавинообразный процесс взаимного открывания приводит к очень быстрому

достижению обоими транзисторами состояния насыщения. Поэтому напряжение Uref, которым запитан по эмиттеру

транзистор Q2, оказывается приложенным к выводу 4 управляющей микросхемы, что приводит к защитному отключению.

Схема защиты от КЗ в нагрузке слаботочных каналов в данном ИБП отсутствует, однако имеется

полная схема защиты от выходных перенапряжений в сильноточных каналах.

Схема защиты от перенапряжения в канале +5В собрана на элементах ZD2, D3, R16. Пока напряжение

на шине +5В не превышает "пробивного" напряжения стабилитрона ZD2 (+5,1В), он заперт. Если этот

уровень будет превышен, стабилитрон ZD2 "пробьется", и в базу транзистора Q1 потечет отпирающий

его ток по цепи: шина +5В - ZD2 - D3 - D2 - 6-э Q1 - "корпус".

Это приведет к "опрокидыванию" бистабильной схемы и защитному отключению.

Аналогичным образом работает и схема контроля перенапряжения на шине +12В, собранная на

элементах ZD1, R17, R16.

Диоды D3, D2 - развязывающие. Они предназначены для исключения влияния выходных сигналов

всех трех защитных схем друг на друга.

Конденсатор С6 устраняет возможность срабатывания защитного отключения при кратковременных

случайных превышениях выходными напряжениями номинальных значений (например, в процессе установления после

возмущающего воздействия в результате работы схемы стабилизации).

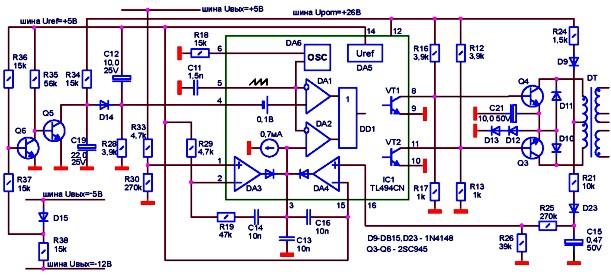

Пример 5.

Комбинированная защита ИБП GT-20QW (рис. 44) включает в себя:

• отключающую схему контроля ширины управляющего импульса;

• неполную схему контроля КЗ в нагрузке;

• неполную схему контроля выходного перенапряжения.

Рисунок 44. Комбинированная защита ИБП GT-200W.

Комбинированная защита в этой схеме построена с использованием двух компараторов микросхемы

IC2 (типа LM339N). Компаратор 1 является элементом схемы контроля ширины управляющего импульса. Компаратор

2 совмещает функции элемента схемы контроля перенапряжения на шине +5В и элемента схемы зашиты от КЗ в

нагрузке слаботочных каналов. Выходы обоих компараторов объединены и воздействуют на состояние пороговой

схемы на транзисторе Q6 по логике "ИЛИ". Открывание выходного транзистора любого из компараторов

1, 2 влечет за собой открывание транзистора Q6 и появление напряжения Uref на выводе 4 управляющей микросхемы

IC1, а значит и защитное отключение. Схема контроля ширины управляющего импульса выполнена как отключающая.

Датчиком ширины управляющего импульса является трансформатор тока СТ, R12 - нагрузка вторичной обмотки

СТ. Переменное прямоугольное импульсное напряжение с резистора R12 выпрямляется по двухполупериод-ной

схеме со средней точкой (диоды D18, D19). С8 - сглаживающая емкость фильтра. R11 - гасящий амплитуду переменного

напряжения резистор. Уровень напряжения на конденсаторе С8 пропорционален ширине управляющих импульсов.

Это напряжение подается в точку А делителя D8, R18, R32, R28 и влияет на распределение потенциалов в узлах

этого делителя. Напряжение с резистора R28 подается на инвертирующий вход компаратора 1 микросхемы IC2.

На неинвертирующий вход этого компаратора подается опорный уровень с резистора R42 делителя R35, R42,

подключенного к шине Uref. Номиналы резисторов обоих делителей подобраны такими, что пока ширина управляющих

импульсов не выходит за диапазон стабилизации, потенциал неинвертирующего входа компаратора 1 (вывод 5)

превышает потенциал его инвертирующего входа (вывод 4). Поэтому выходной транзистор компаратора 1 закрыт.

При повышенном токопотреблении в нагрузке какого-либо из сильноточных каналов ширина управляющих

импульсов начинает возрастать. Поэтому возрастает уровень напряжения на конденсаторе С8, а следовательно,

и на инвертирующем входе компаратора 1. Когда потенциал инвертирующего входа превысит потенциал неинвертирующего

входа, компаратор 1 "опрокинется", выходной транзистор его откроется. В результате этого резистор

R29 базового делителя R30, R29 транзистора Q6 окажется подключен к "корпусу". Поэтому появится

путь для протекания отпирающего базового тока транзистора Q6: шина Uref -э-б Q6 - R29 - к-э выходного

транзистора компаратора 1 - "корпус".

Транзистор Q6 откроется, и напряжение Uref, которым запитан по эмиттеру этот транзистор,

окажется приложенным к выводу 4 управляющей микросхемы IC1 через диод развязки D17. Это, как было показано

ранее, приведет к защитному отключению.

Схема защиты от КЗ в нагрузке слаботочных каналов имеет датчиком традиционный делитель D15,

R45, подключенный между шинами выходных напряжений -5В, -12В. При номинальных уровнях напряжений на этих

шинах потенциал в средней точке этого делителя составляет около -5,8В. Поэтому резистивный делитель R40,

R39 запитывается двуполярно (выходным напряжением +5В и потенциалом -5,8В со средней точки делителя R45,

D15). Напряжение со средней точки делителя R40, R39 подается на инвертирующий вход компаратора 2 микросхемы

IC2 (вывод 8). Номиналы резисторов делителя R40, R39 подобраны такими, что потенциал инвертирующего входа

компаратора 2 (вывод 8) в номинальном режиме меньше, чем потенциал неинвертирующего входа (вывод 9), на

который подан опорный уровень со средней точки делителя R35, R42, подключенного к шине Uref.

При КЗ в нагрузке любого из каналов -5В, -12В потенциал средней точки делителя R45, D15

повышается, и поэтому потенциал инвертирующего входа компаратора 2 начинает превышать потенциал его неинвертирующего

входа. Поэтому компаратор 2 "опрокидывается", выходной транзистор его открывается и появляется

путь для протекания открывающего транзистор Q6 базового тока: шина Uref - э-б Q6 - R29 - к-э выходного

транзистора компаратора 2 - "корпус".

Транзистор Q6 открывается, и напряжение Uref с его эмиттера поступает на вывод 4 управляющей

микросхемы через диод D17, что влечет за собой защитное отключение. Для ускорения "опрокидывания"

система, состоящая из компаратора 2 и транзистора Q6, охвачена положительной обратной связью с помощью

диода D16. Контроль за выходным перенапряжением на шине +5В осуществляется с помощью цепочки D8, R18.

При превышении напряжением на шине +5В расчетного уровня (около +5,1В) соотношение между потенциалами

инвертирующего и неинвертирующего входа компаратора 1 микросхемы IC2 изменяется на противоположное. Компаратор

"опрокидывается", выходной транзистор его открывается, открывается транзистор Q6, и напряжение

Uref с его эмиттера поступает на вывод 4 управляющей микросхемы, что влечет за собой защитное отключение.

Механизм ограничения ширины управляющего импульса здесь не используется. Поэтому усилитель

ошибки DA4 исключается из работы микросхемы традиционным способом: на инвертирующий вход (вывод 15) подано

напряжение Uref, a неинвертирующий вход (вывод 16) заземлен. Следовательно, выходное напряжение усилителя

DA4 независимо от режима, в котором находится схема ИБП, всегда равно 0В и не влияет на работу управляющей

микросхемы IC1.

Пример 6.

Комбинированная защита ИБП SPS-200 (рис. 45) включает в себя:

• ограничивающую схему контроля ширины управляющих импульсов;

• полную схему защиты от КЗ в нагрузке слаботочных каналов;

• неполную схему контроля перенапряжения (только на шине +12В).

Рисунок 45. Комбинированная защита ИБП SPS-200

Ограничивающая схема контроля ширины управляющих импульсов в данной схеме имеет своим датчиком

трансформатор тока СТ, т.е. информация о ширине управляющих импульсов снимается с первичной стороны ИБП.

Резистор R27 является нагрузкой вторичной: обмотки СТ. На нем выделяется знакопеременное импульсное напряжение

прямоугольной формы, обусловленное протеканием пилообразных знакопеременных токовых импульсов через первичную

обмотку СТ. Диоды D14, D15 образуют двухполупериодную схему выпрямления со средней точкой. Выпрямленное

напряжение сглаживается конденсатором С18. Резистор R26 - гасящий амплитуду переменного напряжения. Уровень

напряжения на С18 пропорционален ширине (длительности) токовых импульсов через первичную обмотку СТ, а

значит через первичную обмотку силового импульсного трансформатора и силовые ключи Q1, Q2 инвертора. Длительность

этих импульсов определяется шириной (длительностью) управляющих импульсов на базах силовых ключей. Поэтому

уровень выпрямленного напряжения на конденсаторе С18 будет, в конечном итоге, определяться шириной управляющих

импульсов. При этом диоды D14, D15 включены так, что на конденсаторе С18 образуется отрицательное относительно

"корпуса" напряжение. К инвертирующему входу усилителя ошибки DA4 (вывод 15) подключен резистивный

делитель R30, R28, R31. Потенциалы в узлах А и В этого делителя определяются уровнем напряжения на конденсаторе

С18 (шириной управляющих импульсов), а также уровнем напряжения на шине +5В, Поясним это подробнее. Токи

через резисторы этого делителя протекают по цепям: шина +5В - R30 - R28 - R31 - "корпус", (+)С18

-"корпус" - R31-(-)С18.

Если внимательно проследить эти цепи, то можно увидеть, что через резистор R31 делителя

протекают два встречно направленных тока. Преобладание того или иного из них зависит от соотношения уровней

напряжения на конденсаторе С18 и шине +5В. Номиналы резисторов делителя выбраны такими, что пока ширина

управляющих импульсов не выходит за допустимый предел, определяемый верхней границей диапазона стабилизации,

преобладающим является ток, протекающий с шины +5В. Поэтому на резисторе R31 (в точке А делителя) и конденсаторе

С18 присутствует небольшой положительный потенциал (доли вольта). Потенциал точки В (вывод 15 управляющей

микросхемы) также положителен. Поэтому выходное напряжение усилителя ошибки DA4 равно 0В и не влияет на

работу ШИМ компаратора DA2 и всей микросхемы в целом. При повышенном токопотреблении в нагрузке какого-либо

из сильноточных каналов, когда ширина управляющих импульсов начинает возрастать, происходит увеличение

уровня отрицательного напряжения на конденсаторе С18. Благодаря этому ток разряда С18, протекающий через

R31, начинает преобладать над током с шины +5В через тот же резистор. Другими словами, потенциалы точек

А и В делителя начинают уменьшаться. Когда потенциал точки В станет отрицательным относительно "корпуса",

появится выходное напряжение усилителя DA4, которое будет очень быстро нарастать (усилитель DA4 не охвачен

ООС). С другой стороны, в результате растущего токопотреб-ления в процессе развития КЗ уровень напряжения

на шине +5В несколько уменьшается. Это также способствует снижению потенциалов точек А и В делителя, а

также уменьшению выходного напряжения усилителя ошибки DA3. В момент, когда выходные напряжения усилителей

DA3 и DA4 выравниваются, происходит передача управляющих функций от усилителя DA3 к усилителю DA4, и наступает

ограничение: дальнейшее развитие КЗ в нагрузке не ведет к увеличению ширины управляющих импульсов.

Инвертирующий вход усилителя DA4 (вывод 15) подключен, помимо всего прочего, к шине Uref

через высокоомный резистор R29 (100 кОм). Это делается из тех соображений, что в первый момент после включения

ИБП, когда выходные напряжения еще отсутствуют, на обоих входах усилителя DA4 при отсутствии резистора

R29 оказался бы нулевой потенциал. Состояние выхода DA4, который включен фактически как компаратор (отсутствие

ООС), становилось бы неопределенным, т.е. была бы высока вероятность появления на выходе DA4 высокого

уровня напряжения. Тогда работа ШИМ-компаратора DA2 и всей микросхемы в целом была бы заблокирована сразу

же при включении ИБП в сеть. Чтобы исключить такую возможность, между выводом 15 и шиной Uref включается

высокоомный R29. Поэтому при включении ИВП напряжение Uref, которое появляется раньше, чем выходные напряжения,

прикладывается к делителю R29, R28, R31, и т.к. номинал R29 намного превосходит номиналы R28, R31, на

выводе 15 управляющей микросхемы оказывается небольшой положительный потенциал (доли вольта). Это означает,

что потенциал инвертирующего входа DA4 становится выше потенциала неинвертирующего входа, и усилитель

DA4 принудительно выставляется в состояние 0В на выходе сразу же при включении. Это дает возможность схеме

ИБП выйти в номинальный режим через процесс плавного запуска. В дальнейшем, когда на выходных шинах появятся

напряжения номинального уровня, распределение потенциалов в точках А и В будет определяться уровнями напряжений

на шине +5В и конденсаторе С18, а шина Uref не будет оказывать влияния на это распределение благодаря

высокоомности R29.

Все остальные схемы, входящие в состав этой комбинированной защиты, используют механизм

защитного отключения. При этом воздействие на управляющую микросхему традиционно производится через вывод

4.

Потенциал вывода 4 в установившемся режиме (после завершения процесса плавного запуска)

определяется делителем, в состав которого входят резисторы R39, R34, а также сопротивление участка коллектор-эмиттер

транзистора Q4 и резистор R43. При этом, поскольку база транзисторов Q4 заземлена (т.е. имеет "жесткий"

уровень потенциала 0В), то состояние Q4 (величина сопротивления его участка ко л лектор-эмиттер) будет

определяться потенциалом его эмиттера.

Если этот потенциал будет нулевым или положительным, то Q4 будет закрыт. Если отрицательным

- то Q4 будет находиться в линейном режиме, либо в режиме насыщения (в зависимости от уровня этого отрицательного

потенциала).

Рассмотрим работу схемы защиты от КЗ в нагрузке слаботочных каналов. Датчиком этой схемы

является традиционный диодно-резистивный делитель D20, R47, который подключен между выходными шинами слаботочных

каналов -5В, -12В. Потенциал в средней точке этого делителя является контролируемым сигналом. При нормальном

токопотреблении в нагрузках слаботочных каналов уровень этого сигнала составляет около -5,8В. Это напряжение

подается на делитель R44, R43. Поэтому в средней точке этого делителя, к которой подключен эмиттер транзистора

Q4, присутствует отрицательный потенциал как результат протекания тока делителя по цепи: "корпус"

- R43 - R44 - R47 - шина -12В.

Этот отрицательный потенциал открывает транзистор Q4. Поэтому в режиме нормального токопотребления

потенциал коллектора транзистора Q4, а значит и вывода 4 управляющей микросхемы, близок к 0В. При КЗ в

нагрузке канала -12В либо канала -5В потенциал в средней точке делителя-датчика D20, R47 возрастает до

уровня 0В. Поэтому отрицательный потенциал на резисторе R43 и эмиттере транзистора Q4 исчезает. Транзистор

Q4 закрывается. Напряжение на его коллекторе повышается почти до уровня питающего (Uref) и через диод

развязки D19 прикладывается к выводу 4 управляющей микросхемы, что приводит к защитному отключению.

Схема защиты от КЗ в нагрузке сильноточных каналов реализована на двух компараторах 1 и

2 микросхемы IC2 типа LM339N. На неинвертирующие входы обоих компараторов (выводы 7, 5) подается опорное

напряжение с резистора R54 делителя R55, R54, подключенного к шине Uref. На инвертирующие входы компараторов

подаются контролируемые уровни напряжений с резисторов R59 и R46 делителей-датчиков, подключенных к шинам

+5В и +12В (делитель R58, R59 подключен к шине +5В; делитель R45, R46 - к шине +12В). Номиналы резисторов

всех перечисленных делителей подобраны такими, что при нормальном токопотреблении в нагрузках сильноточных

каналов, потенциалы на инвертирующих входах компараторов 1 и 2 (выводы 6 и 4) превышают опорный потенциал

на их неинвертирующих входах (выводы 7, 5). Поэтому выходные транзисторы обоих компараторов открыты и

выводы 1, 2 микросхемы IC2 подключены к "корпусу" через малое внутреннее сопротивление этих

транзисторов.

При КЗ в нагрузке канала +5В управляющая микросхема сначала, как это было показано выше,

переходит в режим ограничения. Затем, если КЗ продолжает развиваться, уровни выходных напряжений ИБП падают.

Когда они уменьшаться настолько, что потенциал вывода 6 микросхемы IC2 станет меньше потенциала вывода

7, компаратор 1 "опрокинется". Выходной транзистор его закроется, и напряжение Uref окажется

приложенным к делителю R56, D22, D21, R43. Благодаря этому на эмиттере транзистора Q4 окажется положительный

потенциал, представляющий собой падение напряжения на резисторе R43 этого делителя. Транзистор Q4 закрывается,

что приведет к защитному отключению.

При КЗ в нагрузке канала +12В ситуация будет аналогичной, но исполнительным элементом будет

компаратор 2, а делителем-датчиком - делитель R45, R46.

Неполная схема контроля выходного перенапряжения собрана на элементах ZD1, R43 и контролирует

уровень напряжения на шине +12В. При превышении напряжением на этой шине пробивного напряжения стабилитрона

ZD1, последний "пробивается" и потенциал на балластном резисторе R43 повышается как результат

протекания по нему тока стабилитрона. Поэтому на эмиттере транзистора Q4 оказывается положительный потенциал,

и он закрывается, что влечет за собой защитное отключение.

Как следует из всего сказанного выше, для того чтобы управляющая микросхема работала в режиме

ШИМ, необходимо поддерживать транзистор Q4 в открытом состоянии в процессе работы. Для этого на его эмиттере

должен присутствовать отрицательный относительно "корпуса" потенциал. Поскольку этот потенциал

поступает на эмиттер Q4 с выходных шин слаботочных каналов, то становится ясно, что в первый момент после

включения ИБП в сеть, когда выходные напряжения еще отсутствуют, потенциал на эмиттере Q4 будет равен

0В. Однако питающее напряжение на его коллекторе (Uref) уже имеется, и поэтому, если не предпринять специальных

схемных мер, это напряжение через диод D22 окажется приложенным к выводу 4 управляющей микросхемы и заблокирует

ее работу сразу при включении ИБП. Такой схемной мерой, исключающей эту возможность, является транзистор

Q3. Это специальный "пусковой" транзистор, который срабатывает только один раз при каждом включении

ИБП в сеть. Работает он следующим образом.

Сразу после включения в сеть на шине Uep появляется выпрямленное напряжение сети, а затем,

как результат срабатывания схемы пуска, на шине Upom появляется вспомогательное напряжение питания микросхемы.

К этой шине через конденсатор С19 подключен базовый делитель R25, R24 транзистора Q3. Конденсатор С19

был до включения ИБП в сеть полностью разряжен. Поэтому при появлении напряжения на шине Upom все оно

приложится к базовому делителю транзистора Q3, а через управляющий переход транзистора будет протекать

ток зарядки конденсатора С19 по цепи: шина Upom - С19 - R25 -6-э Q3 - "корпус".

Этим током транзистор Q3 открывается до насыщения и потенциал его коллектора, а значит и

потенциал коллектора транзистора Q4 становится равным 0В. Заряд конденсатора С19 будет происходить до

тех пор, пока напряжение на нем не достигнет номинального уровня напряжения Upom (+26B). Когда это случится,

базовый ток через транзистор Q3 перестанет протекать, и он закроется. За это время схема ИБП через процедуру

плавного запуска надежно успевает выйти в номинальный режим. В процессе работы ИБП транзистор Q3 постоянно

закрыт и не влияет на работу схемы.

Однако такое схемное решение предусматривает одно необходимое условие: перед каждым включением

ИБП в сеть конденсатор С19 должен быть полностью разряжен, иначе транзистор Q3 не откроется, и высокое

коллекторное напряжение транзистора Q4 заблокирует работу микросхемы. Для ускорения разрядки конденсатора

С19 после выключения ИБП из сети в схеме предусмотрен диод D11. При этом конденсатор С19 разряжается через

нагрузку шины Upom (внутренние цепи микросхемы и согласующий каскад) и диод D11. Диод D11 уменьшает общее

сопротивление разрядной цепи, т.к. разрядный ток минует базовый делитель R24, R25 транзистора Q3. Поэтому

сокращается время, требуемое для полной разрядки С19, что ускоряет готовность ИБП к последующему включению.

Пример 7.

Комбинированная защита ИБП SP-200W (рис. 46) включает в себя:

• ограничивающую схему контроля ширины управляющих импульсов;

• неполную схему защиты от КЗ в нагрузке (только для слаботочных каналов);

• неполную схему контроля выходного перенапряжения (только на шине +5В).

Эта схема, являясь одной из наиболее сложных, совмещает в себе и нетрадиционный подход к

использованию функциональных узлов управляющей микросхемы TL494.

Рисунок 46. Комбинированная защита ИБП SP-200W

Ограничивающая схема контроля ширины управляющих импульсов имеет своим исполнительным элементом

усилитель ошибки DA4. На неинвертирующий вход этого усилителя подан "жесткий" потенциал 0В (вывод

16 микросхемы соединен с "корпусом"). Потенциал инвертирующего входа усилителя DA4 зависит от

соотношения напряжении на шине +12В и конденсаторе С18. Поясним это подробнее.

На конденсаторе С18 выделяется напряжение отрицательной полярности, полученное в результате

выпрямления переменного напряжения со вторичной обмотки трансформатора тока СТ. Диоды D18, D19 образуют

двухполупериодную схему выпрямления со средней точкой. Уровень отрицательного напряжения на конденсаторе

С18 пропорционален ширине управляющих импульсов. К шине выходного напряжения +12В подключен резистивный

делитель R27, R24, R25, R26. Благодаря тому что конденсатор С18 подключен к точке D этого делителя, через

резистор R26 протекают два встречно направленных тока по цепям: шина +12 В - R27 - R24 - R25 - R26 -"корпус"-

(+)С18- "корпус"- R26- (-)С18.

Номиналы резисторов делителя подобраны такими, что пока токопотребление сильноточных каналов

(а значит, и ширина управляющих импульсов) находится в диапазоне стабилизации, преобладающим является

ток, протекающий через резистор R26 с шины +12В. Поэтому в точках С и D делителя в нормальном режиме работы

присутствуют положительные потенциалы. Выходное напряжение усилителя DA4 равно 0В, и он не влияет на работу

микросхемы. В случае значительного возрастания ширины управляющих импульсов с выходом за диапазон стабилизации

выпрямленное отрицательное напряжение на конденсаторе С18 начинает увеличиваться (по абсолютной величине).

Потенциалы всех узлов делителя R27, R24, R25, R26 начинают уменьшаться. Как только потенциал в точке С

этого делителя станет равен 0В, появится выходное напряжение усилителя DA4. Попутно отметим, что преобладающим

током через резистор R26 делителя становится ток разрядки конденсатора С18. Поэтому в точке D делителя

потенциал будет отрицательным. При дальнейшем росте ширины управляющих импульсов выходное напряжение усилителя

DA4 начинает расти, а выходное напряжение усилителя DA3 несколько уменьшается. Когда эти напряжения сравниваются,

то управление ШИМ-компаратором DA2 передается от усилителя DA3 к усилителю DA4, и микросхема переходит

в режим ограничения.

Построение схемы зашиты от КЗ в нагрузке слаботочных каналов в данной схеме является оригинальным

и заслуживает особого внимания как встречающееся достаточно редко. Механизм срабатывания защиты остается

тем же, что и в предыдущих схемах, однако в качестве исполнительного элемента здесь используется не компаратор

"мертвой" зоны DA1, а ШИМ-компаратор DA2. Компаратор DA1 в этой схеме выполняет лишь функцию

плавного запуска совместно с формирующей цепочкой R14, R15, С8. Принцип ее действия рассмотрен в разделе,

посвященном проблеме плавного запуска.

Датчиком, контролирующим уровни напряжений на шинах слаботочных каналов -5В, -12В, является

делитель D23, R32. При этом в нормальном режиме работы потенциал в средней точке этого делителя составляет

-5,8В, т.к. через делитель протекает ток по цепи: шина -5В - D23 - R32 -шина - 12В.

Потенциал средней точки этого делителя всегда будет ниже потенциала шины -5В на величину

прямого падения напряжения на диоде D23. Контролируемый сигнал со средней точки делителя подается на вход

трехкаскадного УПТ (связь между всеми каскадами гальваническая).

Первый каскад выполнен на транзисторе Q6, который включен по схеме с общей базой. Коллекторной

нагрузкой Q6 является резистор R30, последовательно с которым включен диод D22. Контролируемый сигнал

подается на эмиттер транзистора Q6 через резистор R31. Усиленный сигнал снимается с коллектора транзистора

Q6 на базу транзистора Q5 второго каскада. Диод D22 включается для компенсации температурного дрейфа параметров

транзистора Q5. Поясним это подробнее.

При увеличении температуры ток через управляющий переход транзистора Q5 возрастает. Это

приводит к дополнительному открыванию Q5, которое не связано с изменением контролируемого сигнала в средней

точке делителя-датчика D23, R32, а следовательно, неправильной работе всей схемы в целом. Диод D22, обладающий

такой же температурной зависимостью вольтампер-ной характеристики, как и управляющий переход транзистора

Q5, включается параллельно этому переходу и оказывает компенсирующее воздействие на ток через переход.

При увеличении температуры динамическое сопротивление диода D22 уменьшится, поэтому уменьшится и падение

напряжения на нем. Ток же через диод останется практически неизменным, т.к. определяется состоянием (степенью

приоткрывайия) транзистора Q6. Поэтому суммарное падение напряжения на цепочке R30, D22 станет меньше.

Поскольку это уменьшившееся падение напряжения прикладывается к цепочке, состоящей из резистора R28 и

управляющего перехода транзистора Q5, то ток через эту цепочку останется неизменным, несмотря на уменьшившееся

динамическое сопротивление эмиттерного перехода транзистора Q5.

Питание первого каскада УПТ осуществляется с шины выходного напряжения +5В.

Второй каскад УПТ собран на транзисторе Q5, который включен по схеме с общим эмиттером.

Резистор R28 в эмиттерной цепи - токозадаю-щий. Коллекторной нагрузкой транзистора Q5 является резистор

R29. Питание второго каскада УПТ также осуществляется с шины +5В. Усиленный сигнал снимается с резистора

R29 и подается на базовый для транзистора Q7 делитель R33, R34 через диод R21.

Третий каскад УПТ собран на транзисторе Q7, который включен по схеме с общим эмиттером.

Коллекторной нагрузкой Q7 является резистор R35. Питание каскада осуществляется с шины вспомогательного

напряжения питания управляющей микросхемы Upom. Базовый делитель транзистора Q7 состоит из резисторов

R27, R33, R34 и подключен к шине +12В. Усиленный сигнал снимается с коллекторной нагрузки Q7 и подается

на пороговую схему, собранную на элементах С19, ZD2. Сигнал с выхода пороговой схемы управляет состоянием

бистабильной схемы на транзисторах Q8, Q9, т.к. подается на вход этой схемы (на базу транзистора Q9).

Транзистор Q8 бистабильной схемы запитывается по эмиттеру напряжением Uref. Бистабильная схема, в свою

очередь, управляет работой управляющей микросхемы IC1, т.к. выход ее (коллектор транзистора Q8) через

диод D24 подключен к выводу 3 управляющей микросхемы (другими словами, к неинвертирующему входу ШИМ-компаратора

DA2). Проследим динамику работы этой схемы.

В режиме нормального токопотребления в нагрузках слаботочных каналов потенциал в средней

точке делителя-датчика D23, R32 составляет -5,8В. Поэтому транзистор Q6 открыт, а значит открыт и транзистор

Q5. Потенциал на коллекторе транзистора Q5 максимален и за вычетом падения напряжения на низкоомном R28

почти равен питающему напряжению +5В. Поэтому диод D21 максимально подзакрыт, и потенциал его анода максимален.

Другими словами, цепочка D21, R29 оказывает минимальное шунтирующее воздействие на базовый для транзистора

Q7 делитель R33, R34. Поэтому транзистор Q7 максимально приоткрыт, и напряжение на его коллекторе имеет

некоторое минимальное значение, не превышающее пробивное напряжение стабилитрона ZD2 (12В). Поэтому стабилитрон

заперт, и закрыты оба транзистора Q8, Q9 бистабильной схемы. Напряжение на аноде развязывающего диода

D24 равно 0В. Поэтому диод D24 заперт, т.к. на его катоде присутствует положительное выходное напряжение

усилителя ошибки DA3. Таким образом вся защитная схема не влияет на работу управляющей микросхемы.

При КЗ в нагрузке канала -12В диод D23 делителя-датчика запирается, т.к. потенциал его катода

(0В) становится выше потенциала анода (-5В). Поэтому нулевым смещением эмиттерного перехода закрывается

транзистор Q6 первого каскада УПТ. Закрывание транзистора Q6 влечет за собой закрывание транзистора Q5

и, следовательно, уменьшение напряжения на его коллекторе. Поэтому открывается в максимальной степени

диод D21 и цепочка D21, R29 начинает оказывать максимальное шунтирующее воздействие на базовый для транзистора

Q7 делитель R33, R34. Поэтому транзистор Q7 подзакрывается. Напряжение на его коллекторе возрастает. Когда

это напряжение превысит пробивное напряжение стабилитрона ZD2, последний пробивается и через него в базу

транзистора Q9 начинает протекать ток по цепи: шина Upom - R35 - ZD2 - D25 -б-э09- "корпус".

Поэтому транзистор Q9 приоткрывается, что влечет за собой лавинообразный процесс взаимного

открывания обоих транзисторов Q9, Q8 бистабильной схемы (благодаря наличию ПОС). Транзисторы Q8, Q9 почти

мгновенно достигают состояния насыщения, и напряжение Uref оказывается приложенным к выводу 3 управляющей

микросхемы через малое внутреннее сопротивление открытого Q8 и диод D24. Таким образом на неинвертирующем

входе ШИМ-компаратора DA2 оказывается высокий уровень напряжения (около +4В), который превышает амплитуду

пилообразного напряжения, подаваемого на инвертирующий вход этого компаратора с выхода генератора DA6.

Поэтому компаратор DA2 перестает переключаться. На выходе его появляется постоянная логическая "1",

которая повторяясь элементом DD1, приводит к останову работы всего цифрового тракта микросхемы. Другими

словами, происходит защитное отключение. При этом ШИМ-компаратор DA2 в аварийной ситуации ведет себя точно

так же, как и компаратор "мертвой" зоны DA1 в ранее рассмотренных схемах, чем и обусловлена

возможность его использования в качестве исполнительного элемента защиты.

При КЗ в нагрузке канала -5В диод D23 делителя-датчика будет открыт, однако потенциал его

катода будет составлять всего около -0,8В. Поэтому транзистор Q6 первого каскада УПТ будет фактически

закрыт, и механизм срабатывания защиты будет тем же самым.

Конденсатор С19 выполняет в схеме демпфирующую функцию и предотвращает ложное срабатывание

защиты при кратковременных возможных "выбросах" напряжения на шине Upom, a также при кратковременных

возможных "провалах" напряжения на шинах -12 и -5В.

Резисторы R38, R39 и R37, R36 образуют базовые делители для транзисторов Q8 и Q9 соответственно.

Диоды D21, D25, D24 - развязывающие.

В схему рисунка входит также и схема защиты от выходного перенапряжения на шине +5В. Она

собрана на элементах ZD1, R54, D26, R56, С20. Выход этой схемы так же,как и выход пороговой схемы токовой

защиты, подключен ко входу бистабильной схемы (к базе транзистора Q9). Стабилитрон ZD1 имеет пробивное

напряжение 5,1В. Поэтому пока напряжение на шине +5В не превышает этого значения, стабилитрон ZD1 заперт.

Поэтому закрыты оба транзистора бистабильной схемы. При возникновении перенапряжения на шине +5В стабилитрон

ZD1 "пробивается", и через него протекает ток по цепи: шина +5В - ZD1 -R54 - "корпус".

Этот ток вызывает появление падения напряжения на балластном для ZD1 резисторе R54. Падение

напряжения с резистора R54 прикладывается к управляющему переходу транзистора Q9 бистабилыюй схемы через

диод D26 и резистор R56. Поэтому в базу Q9 начинает протекать ток, приоткрывающий его. Далее развивается

лавинообразный процесс взаимного открывания транзисторов Q9, Q8, что приводит к появлению высокого уровня

напряжения на неинвертирующем входе ШИМ-компаратора DA2, а значит, к защитному отключению.

Конденсатор С20 предназначен для подавления кратковременных импульсных помех на шине +5В,

и т.о. предотвращает ложное срабатывание защиты, т.е. выполняет демпфирующую функцию, как и конденсатор

С19.

Как следует из приведенных примеров, схемотехническая реализация комбинированных защит весьма

разнообразна. Большим разнообразием отличается и применяемая элементная база (транзисторы, тиристоры,

микросхемы, опорные диоды и т.д.). Авторы не претендуют на абсолютную полноту возможных схемотехнических

решений, которые приведены в этой книге. На практике могут встречаться и другие решения, которые, однако,

реализуют те же самые идеи. Поэтому при анализе каждой конкретной схемы ИБП в части построения комбинированной

защиты, можно, опираясь на приведенную в этом разделе классификацию, выяснить назначение тех или иных

элементов этой схемы и всей схемы в целом.

Завершая раздел, посвященный анализу комбинированных защит, необходимо отметить, что построение

каждой конкретной защитной схемы вплотную увязано с построением других функциональных узлов ИБП, таких

как схема возбуждения, схема стабилизации, схема получения выходных напряжений и т.д. Другими словами,

все функциональные узлы конкретной схемы ИБП работают согласованно и взаимосвязаны друг с другом. Поэтому

для уяснения всей картины в целом, необходимо не только представлять себе назначение и работу отдельных

функциональных узлов, но и их взаимосвязь и взаимное влияние. В связи с этим необходимо четко представлять

себе последовательность и физику процессов, происходящих в ИБП:

• при включении его в питающую сеть;

• при выключении его из питающей сети;

• при возникновении аварийной ситуации, обусловленной КЗ в нагрузке какого-либо из выходных

каналов, либо перенапряжением на выходе какого-либо из этих каналов;

• при возмущениях, приводящих к отклонению выходных напряжений ИБП от номинальных значений

в пределах диапазона стабилизации.

Все эти последовательности называются алгоритмами. Рассмотрению алгоритма включения ИБП

в питающую сеть посвящен следующий раздел этой книги.

Адрес администрации сайта: admin@soundbarrel.ru

|