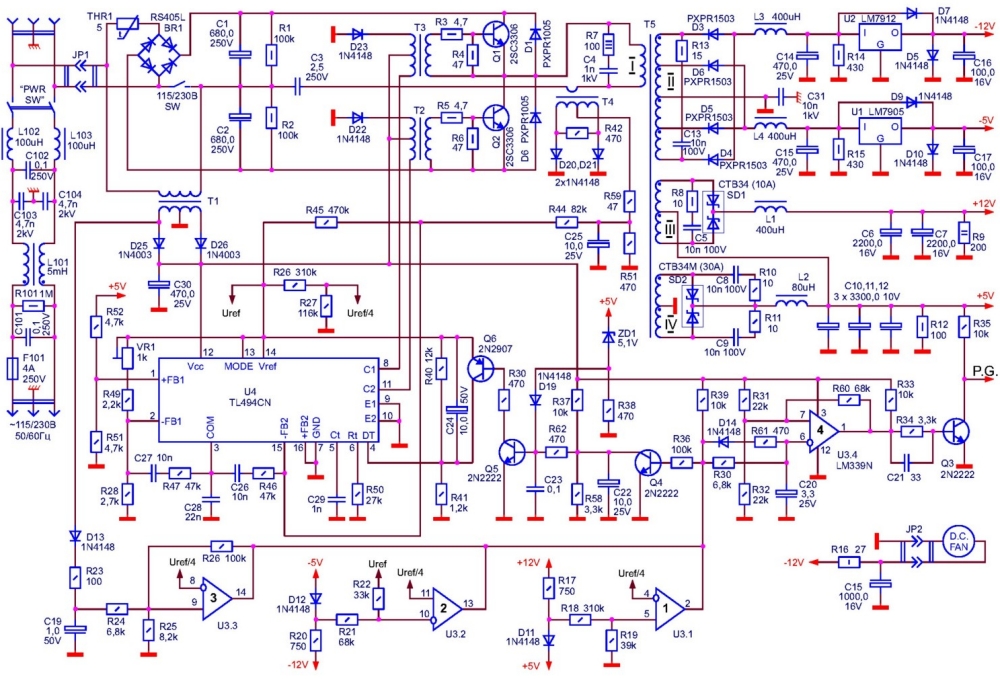

ПРИНЦИПИАЛЬНАЯ СХЕМА ИМПУЛЬСНОГО БЛОКА ПИТАНИЯ

КОМПЬЮТЕРА

СТАТЬЯ ПОДГОТОВЛЕНА НА ОСНОВЕ КНИГИ А. В. ГОЛОВКОВА и В. Б ЛЮБИЦКОГО "БЛОКИ ПИТАНИЯ ДЛЯ СИСТЕМНЫХ МОДУЛЕЙ ТИПА IBM PC-XT/AT" ИЗДАТЕЛЬСТВА «ЛАД и Н»

ПРИМЕР ПОСТРОЕНИЯ ОДНОГО ИЗ ИМПУЛЬСНЫХ БЛОКОВ ПИТАНИЯ

Подводя итог всему сказанному, для полноты картины приведем в качества примера полное описание

принципиальной схемы для одного из 200-ваттных импульсных блоков питания (производство Тайвань PS6220C)

(рис. 56).

Переменное напряжение сети подается через сетевой выключатель PWR SW через сетевой предохранитель

F101 4А, помехоподавляющие фильтры, образованные элементами С101, R101, L101, С104, С103, С102 и дроссели

И 02, L103 на:

• выходной трехконтактный разъем, к которому может подстыковываться кабель питания дисплея;

• двухконтактный разъем JP1, ответная часть которого находится на плате.

С разъема JP1 переменное напряжение сети поступает на:

• мостовую схему выпрямления BR1 через терморезистор THR1;

• первичную обмотку пускового трансформатора Т1.

Рисунок 56. Схема электрическая принципиальная импульсного блока питания ИБП PS-6220C

На выходе выпрямителя BR1 включены сглаживающие емкости фильтра С1, С2. Терморезистор THR

ограничивает начальный бросок зарядного тока этих конденсаторов. Переключатель 115V/230V SW обеспечивает

возможность питания импульсного блока питания как от сети 220-240В, так и от сети 110/127 В.

Высокооомные резисторы R1, R2, шунтирующие конденсаторы С1, С2 являются симметрирующими

(выравнивают напряжения на С1 и С2), а также обеспечивают разрядку этих конденсаторов после выключения

импульсного блока питания из сети. Результатом работы входных цепей является появление на шине выпрямленного

напряжения сети постоянного напряжения Uep, равного +310В, с некоторыми пульсациями. В данном импульсном

блоке питания используется схема запуска с принудительным (внешним) возбуждением, которая реализована

на специальном пусковом трансформаторе Т1, на вторичной обмотке которого после включения блока питания

в сеть появляется переменное напряжение с частотой питающей сети. Это напряжение выпрямляется диодами

D25, D26, которые образуют со вторичной обмоткой Т1 двухполупериодную схему выпрямления со средней точкой.

СЗО - сглаживающая емкость фильтра, на которой образуется постоянное напряжение, используемое для питания

управляющей микросхемы U4.

В качестве управляющей микросхемы в данном импульсном блоке питания традиционно используется

ИМС TL494.

Питающее напряжение с конденсатора СЗО подается на вывод 12 U4. В результате на выводе 14

U4 появляется выходное напряжение внутреннего опорного источника Uref=-5B, запускается внутренний генератор

пилообразного напряжения микросхемы, а на выводах 8 и 11 появляются управляющие напряжения, которые представляют

собой последовательности прямоугольных импульсов с отрицательными передними фронтами, сдвинутые друг относительно

друга на половину периода. Элементы С29, R50, подключенные к выводам 5 и 6 микросхемы U4 определяют частоту

пилообразного напряжения, вырабатываемого внутренним генератором микросхемы.

Согласующий каскад в данном импульсном блоке питания выполнен по бестранзисторной схеме

с раздельным управлением. Напряжение питания с конденсатора СЗО подается в средние точки первичных обмоток

управляющих трансформаторов Т2, ТЗ. Выходные транзисторы ИМС U4 выполняют функции транзисторов согласующего

каскада и включены по схеме с ОЭ. Эмиттеры обоих транзисторов (выводы 9 и 10 микросхемы) подключены к

"корпусу". Коллекторными нагрузками этих транзисторов являются первичные полуобмотки управляющих

трансформаторов Т2, ТЗ, подключенные к выводам 8, 11 микросхемы U4 (открытые коллекторы выходных транзисторов).

Другие половины первичных обмоток Т2, ТЗ с подключенными к ним диодами D22, D23 образуют цепи размагничивания

сердечников этих трансформаторов.

Трансформаторы Т2, ТЗ управляют мощными транзисторами полумостового инвертора.

Переключения выходных транзисторов микросхемы вызывают появление импульсных управляющих

ЭДС на вторичных обмотках управляющих трансформаторов Т2, ТЗ. Под действием этих ЭДС силовые транзисторы

Q1, Q2 попеременно открываются с регулируемыми паузами ("мертвыми зонами"). Поэтому через первичную

обмотку силового импульсного трансформатора Т5 протекает переменный ток в виде пилообразных токовых импульсов.

Это объясняется тем, что первичная обмотка Т5 включена в диагональ электрического моста, одно плечо которого

образовано транзисторами Q1, Q2, а другое - конденсаторами С1, С2. Поэтому при открывании какого-либо

из транзисторов Q1, Q2 первичная обмотка Т5 оказывается подключена к одному из конденсаторов С1 или С2,

что и обуславливает протекание через нее тока в течение всего времени, пока открыт транзистор.

Демпферные диоды D1, D2 обеспечивают возврат энергии, запасенной в индуктивности рассеяния

первичной обмотки Т5 за время закрытого состояния транзисторов Q1, Q2 обратно в источник (рекуперация).

Цепочка С4, R7, шунтирующая первичную обмотку Т5, способствует подавлению высокочастотных

паразитных колебательных процессов, которые возникают в контуре, образованном индуктивностью первичной

обмотки Т5 и ее меж-витковой емкостью, при закрываниях транзисторов Q1, Q2, когда ток через первичную

обмотку резко прекращается.

Конденсатор СЗ, включенный последовательно с первичной обмоткой Т5, ликвидирует постоянную

составляющую тока через первичную обмотку Т5, исключая тем самым нежелательное подмагничивание его сердечника.

Резисторы R3, R4 и R5, R6 образуют базовые делители для мощных транзисторов Q1, Q2 соответственно

и обеспечивают оптимальный режим их переключения с точки зрения динамических потерь мощности на этих транзисторах.

Протекание переменного тока через первичную обмотку Т5 обуславливает наличие знакопеременных

прямоугольных импульсных ЭДС на вторичных обмотках этого трансформатора.

Силовой трансформатор Т5 имеет три вторичные обмотки, каждая из которых имеет вывод от средней

точки.

Обмотка IV обеспечивает получение выходного напряжения +5В. Диодная сборка SD2 (полумост)

образует с обмоткой IV двухполупериодную схему выпрямления со средней точкой (средняя точка обмотки IV

заземлена).

Элементы L2, СЮ, С11, С12 образуют сглаживающий фильтр в канале +5В.

Для подавления паразитных высокочастотных колебательных процессов, возникающих при коммутациях

диодов сборки SD2, эти диоды за-шунтированы успокаивающими RC-цепочками С8, R10nC9, R11.

Диоды сборки SD2 представляют собой диоды с барьером Шоттки, чем достигается необходимое

быстродействие и повышается КПД выпрямителя.

Обмотка III совместно с обмоткой IV обеспечивает получение выходного напряжения +12В вместе

с диодной сборкой (полумостом) SD1. Эта сборка образует с обмоткой III двухполупериодную схему выпрямления

со средней точкой. Однако средняя точка обмотки III не заземлена, а подключена к шине выходного напряжения

+5В. Это даст возможность использовать диоды Шоттки в канале выработки +12В, т.к. обратное напряжение,

прикладываемое к диодам выпрямителя при таком включении, уменьшается до допустимого для диодов Шоттки

уровня.

Элементы L1, С6, С7 образуют сглаживающий фильтр в канале +12В.

Резисторы R9, R12 предназначены для ускорения разрядки выходных конденсаторов шин +5В и

+12В после выключения ИБП из сети.

RC-цепочка С5, R8 предназначена для подавления колебательных процессов, возникающих в паразитном

контуре, образованном индуктивностью обмотки III и ее межвитковой емкостью.

Обмотка И с пятью отводами обеспечивает получение отрицательных выходных напряжений -5В

и-12В.

Два дискретных диода D3, D4 образуют полумост двухполупериодного выпрямления в канале выработки

-12В, а диоды D5, D6 - в канале -5В.

Элементы L3, С14 и L2, С12 образуют сглаживающие фильтры для этих каналов.

Обмотка II, также как и обмотка III, зашунтиро-вана успокоительной RC-цепочкой R13, С13.

Средняя точка обмотки II заземлена.

Стабилизация выходных напряжений осуществляются разными способами в разных каналах.

Отрицательные выходные напряжения -5В и -12В стабилизируются при помощи линейных интегральных

трехвыводных стабилизаторов U4 (типа 7905) и U2 (типа 7912).

Для этого на входы этих стабилизаторов подаются выходные напряжения выпрямителей с конденсаторов

С14, С15. На выходных конденсаторах С16, С17 получаются стабилизированные выходные напряжения -12В и -5В.

Диоды D7, D9 обеспечивают разрядку выходных конденсаторов С16, С17 через резисторы R14,

R15 после выключения импульсного блока питания из сети. Иначе эти конденсаторы разряжались бы через схему

стабилизаторов, что нежелательно.

Через резисторы R14, R15 разряжаются и конденсаторы С14, С15.

Диоды D5, D10 выполняют защитную функцию в случае пробоя выпрямительных диодов.

Если хотя бы один из этих диодов (D3, D4, D5 или D6) окажется "пробитым", то в

отсутствие диодов D5, D10 ко входу интегрального стабилизатора U1 (или U2) прикладывалось бы положительное

импульсное напряжение, а через электролитические конденсаторы С14 или С15 протекал бы переменный ток,

что привело бы к выходу их из строя.

Наличие диодов D5, D10 в этом случае устраняет возможность возникновения такой ситуации,

т.к. ток замыкается через них.

Например, в случае, если "пробит" диод D3, положительная часть периода, когда

D3 должен быть закрыт, ток замкнется по цепи: к-а D3 - L3 -D7- D5- "корпус".

Стабилизация выходного напряжения +5В осуществляется методом ШИМ. Для этого к шине выходного

напряжения +5В подключен измерительный резистивный делитель R51, R52. Сигнал, пропорциональный уровню

выходного напряжения в канале +5В, снимается с резистора R51 и подается на инвертирующий вход усилителя

ошибки DA3 (вывод 1 управляющей микросхемы). На прямой вход этого усилителя (вывод 2) подается опорный

уровень напряжения, снимаемый с резистора R48, входящего в делитель VR1, R49, R48, который подключен к

выходу внутреннего опорного источника микросхемы U4 Uref=+5B. При изменениях уровня напряжения на шине

+5В под воздействием различных дестабилизирующих факторов происходит изменение величины рассогласования

(ошибки) между опорным и контролируемым уровнями напряжения на входах усилителя ошибки DA3. В результате

ширина (длительность) управляющих импульсов на выводах 8 и 11 микросхемы U4 изменяется таким образом,

чтобы вернуть отклонившееся выходное напряжение +5В к номинальному значению (при уменьшении напряжения

на шине +5В ширина управляющих импульсов увеличивается, а при увеличении этого напряжения -уменьшается).

Устойчивая (без возникновения паразитной генерации) работа всей петли регулирования обеспечивается

за счет цепочки частотно-зависимой отрицательной обратной связи, охватывающей усилитель ошибки DA3. Эта

цепочка включается между выводами 3 и 2 управляющей микросхемы U4 (R47, С27).

Выходное напряжение +12В в данном ИБП не стабилизируется.

Регулировка уровня выходных напряжений в данном ИБП производится только для каналов +5В

и +12В. Эта регулировка осуществляется за счет изменения уровня опорного напряжения на прямом входе усилителя

ошибки DA3 при помощи подстроечного резистора VR1.

При изменении положения движка VR1 в процессе настройки ИБП будет изменяться в некоторых

пределах уровень напряжения на шине +5В, а значит и на шине +12В, т.к. напряжение с шины +5В подается

в среднюю точку обмотки III.

Комбинированная зашита данного ИБП включает в себя:

• ограничивающую схему контроля ширины управляющих импульсов;

• полную схему защиты от КЗ в нагрузках;

• неполную схему контроля выходного перенапряжения (только на шине +5В).

Рассмотрим каждую из этих схем.

Ограничивающая схема контроля использует в качестве датчика трансформатор тока Т4, первичная

обмотка которого включена последовательно с первичной обмоткой силового импульсного трансформатора Т5.

Резистор R42 является нагрузкой вторичной обмотки Т4, а диоды D20, D21 образуют двухпо-лупериодную

схему выпрямления знакопеременного импульсного напряжения, снимаемого с нагрузки R42.

Резисторы R59, R51 образуют делитель. Часть напряжения сглаживается конденсатором С25. Уровень

напряжения на этом конденсаторе пропорционально зависит от ширины управляющих импульсов на базах силовых

транзисторов Q1, Q2. Этот уровень через резистор R44 подается на инвертирующий вход усилителя ошибки DA4

(вывод 15 микросхемы U4). Прямой вход этого усилителя (вывод 16) заземлен. Диоды D20, D21 включены так,

что конденсатор С25 при протекании тока через эти диоды заряжается до отрицательного (относительно общего

провода) напряжения.

В нормальном режиме работы, когда ширина управляющих импульсов не выходит за допустимые

пределы, потенциал вывода 15 положителен, благодаря связи этого вывода через резистор R45 с шиной Uref.

При чрезмерном увеличении ширины управляющих импульсов по какой-либо причине, отрицательное напряжение

на конденсаторе С25 возрастает, и потенциал вывода 15 становится отрицательным. Это приводит к появлению

выходного напряжения усилителя ошибки DA4, которое до этого было равно 0В. Дальнейший рост ширины управляющих

импульсов приводит к тому, что управление переключениями ШИМ-ком-паратора DA2 передается к усилителю DA4,

и последующего за этим увеличения ширины управляющих импульсов уже не происходит (режим ограничения),

т.к. ширина этих импульсов перестает зависеть от уровня сигнала обратной связи на прямом входе усилителя

ошибки DA3.

Схема защиты от КЗ в нагрузках условно может быть разделена на защиту каналов выработки

положительных напряжений и защиту каналов выработки отрицательных напряжений, которые схемотехнически

реализованы примерно одинаково.

Датчиком схемы защиты от КЗ в нагрузках каналов выработки положительных напряжений (+5В

и +12В) является диодно-резистивный делитель D11, R17, подключенный между выходными шинами этих каналов.

Уровень напряжения на аноде диода D11 является контролируемым сигналом. В нормальном режиме работы, когда

напряжения на выходных шинах каналов +5В и +12В имеют номинальные величины, потенциал анода диода D11

составляет около +5,8В, т.к. через делитель-датчик протекает ток с шины +12В на шину +5В по цепи: шина

+12В - R17- D11 - шина +56.

Контролируемый сигнал с анода D11 подается на резистивный делитель R18, R19. Часть этого

напряжения снимается с резистора R19 и подается на прямой вход компаратора 1 микросхемы U3 типа LM339N.

На инвертирующий вход этого компаратора подается опорный уровень напряжения с резистора R27 делителя R26,

R27, подключенного к выходу опорного источника Uref=+5B управляющей микросхемы U4. Опорный уровень выбран

таким, чтобы при нормальном режиме работы потенциал прямого входа компаратора 1 превышал бы потенциал

инверсного входа. Тогда выходной транзистор компаратора 1 закрыт, и схема ИБП нормально функционирует

в режиме ШИМ.

В случае КЗ в нагрузке канала +12В, например, потенциал анода диода D11 становится равным

0В, поэтому потенциал инвертирующего входа компаратора 1 станет выше, чем потенциал прямого входа, и выходной

транзистор компаратора откроется. Это вызовет закрывание транзистора Q4, который нормально открыт током

базы, протекающим по цепи: шина Upom - R39 - R36 -б-э Q4 - "корпус".

Открывание выходного транзистора компаратора 1 подключает резистор R39 к "корпусу",

и поэтому транзистор Q4 пассивно закрывается нулевым смещением. Закрывание транзистора Q4 влечет за собой

зарядку конденсатора С22, который выполняет функцию звена задержки срабатывания защиты. Задержка необходима

из тех соображений, что в процессе выхода ИБП на режим, выходные напряжения на шинах +5В и +12В появляются

не сразу, а по мере зарядки выходных конденсаторов большой емкости. Опорное же напряжение от источника

Uref, напротив, появляется практически сразу же после включения ИБП в сеть. Поэтому в пусковом режиме

компаратор 1 переключается, его выходной транзистор открывается, и если бы задерживающий конденсатор С22

отсутствовал, то это привело бы к срабатыванию защиты сразу при включении ИБП в сеть. Однако в схему включен

С22, и срабатывание защиты происходит лишь после того как напряжение на нем достигнет уровня, определяемого

номиналами резисторов R37, R58 делителя, подключенного к шине Upom и являющегося базовым для транзистора

Q5. Когда это произойдет, транзистор Q5 открывается, и резистор R30 оказывается подключен через малое

внутреннее сопротивление этого транзистора к "корпусу". Поэтому появляется путь для протекания

тока базы транзистора Q6 по цепи: Uref - э-6 Q6 - R30 - к-э Q5 -"корпус".

Транзистор Q6 открывается этим током до насыщения, в результате чего напряжение Uref=5B,

которым запитан по эмиттеру транзистор Q6, оказывается приложенным через его малое внутреннее сопротивление

к выводу 4 управляющей микросхемы U4. Это, как было показано ранее, ведет к останову работы цифрового

тракта микросхемы, пропаданию выходных управляющих импульсов и прекращению переключении силовых транзисторов

Q1, Q2, т.е. к защитному отключению. КЗ в нагрузке канала +5В приведет к тому, что потенциал анода диода

D11 будет составлять всего около +0.8В. Поэтому выходной транзистор компаратора (1) окажется открыт, и

произойдет защитное отключение.

Аналогичным образом построена защита от КЗ в нагрузках каналов выработки отрицательных напряжений

(-5В и -12В) на компараторе 2 микросхемы U3. Элементы D12, R20 образуют диодно-резистивный делитель-датчик,

подключаемый между выходными шинами каналов выработки отрицательных напряжений. Контролируемым сигналом

является потенциал катода диода D12. При КЗ в нагрузке канала -5В или -12В, потенциал катода D12 повышается

(от -5,8 до 0В при КЗ в нагрузке канала -12В и до -0,8В при КЗ в нагрузке канала -5В). В любом из этих

случаев открывается нормально закрытый выходной транзистор компаратора 2, что и обуславливает срабатывание

защиты по приведенному выше механизму. При этом опорный уровень с резистора R27 подается на прямой вход

компаратора 2, а потенциал инвертирующего входа определяется номиналами резисторов R22, R21. Эти резисторы

образуют двуполярно запитанный делитель (резистор R22 подключен к шине Uref=+5B, а резистор R21 - к катоду

диода D12, потенциал которого в нормальном режиме работы ИБП, как уже отмечалось, составляет -5,8В). Поэтому

потенциал инвертирующего входа компаратора 2 в нормальном режиме работы поддерживается меньшим, чем потенциал

прямого входа, и выходной транзистор компаратора будет закрыт.

Защита от выходного перенапряжения на шине +5В реализована на элементах ZD1, D19, R38, С23.

Стабилитрон ZD1 (с пробивным напряжением 5,1В) подключается к шине выходного напряжения +5В. Поэтому,

пока напряжение на этой шине не превышает +5,1 В, стабилитрон закрыт, а также закрыт транзистор Q5. В

случае увеличения напряжения на шине +5В выше +5,1В стабилитрон "пробивается", и в базу транзистора

Q5 течет отпирающий ток, что приводит к открыванию транзистора Q6 и появлению напряжения Uref=+5B на выводе

4 управляющей микросхемы U4, т.е. к защитному отключению. Резистор R38 является балластным для стабилитрона

ZD1. Конденсатор С23 предотвращает срабатывание защиты при случайных кратковременных выбросах напряжения

на шине +5В (например, в результате установления напряжения после скачкообразного уменьшения тока нагрузки).

Диод D19 является развязывающим.

Схема образования сигнала PG в данном импульсном блоке питания является двухфункциональной

и собрана на компараторах (3) и (4) микросхемы U3 и транзисторе Q3.

Схема построена на принципе контроля наличия переменного низкочастотного напряжения на вторичной

обмотке пускового трансформатора Т1, которое действует на этой обмотке лишь при наличии питающего напряжения

на первичной обмотке Т1, т.е. пока импульсный блок питания включен в питающую сеть.

Практически сразу после включения ИБП в питающую сеть появляется вспомогательное напряжение

Upom на конденсаторе СЗО, которым запитывается управляющая микросхема U4 и вспомогательная микросхема

U3. Кроме того, переменное напряжение со вторичной обмотки пускового трансформатора Т1 через диод D13

и то-коограничивающий резистор R23 заряжает конденсатор С19. Напряжением с С19 запитывается резистивный

делитель R24, R25. С резистора R25 часть этого напряжения подается на прямой вход компаратора 3, что приводит

к закрыванию его выходного транзистора. Появляющееся сразу вслед за этим выходное напряжение внутреннего

опорного источника микросхемы U4 Uref=+5B за-питывает делитель R26, R27. Поэтому на инвертирующий вход

компаратора 3 подается опорный уровень с резистора R27. Однако этот уровень выбран меньшим, чем уровень

на прямом входе, и поэтому выходной транзистор компаратора 3 остается в закрытом состоянии. Поэтому начинается

процесс зарядки задерживающей емкости С20 по цепи: Upom - R39 - R30 - С20 - "корпус".

Растущее по мере зарядки конденсатора С20 напряжение подается на инверсный вход 4 микросхемы

U3. На прямой вход этого компаратора подается напряжение с резистора R32 делителя R31, R32, подключенного

к шине Upom. Пока напряжение на заряжающемся конденсаторе С20 не превышает напряжения на резисторе R32,

выходной транзистор компаратора 4 закрыт. Поэтому в базу транзистора Q3 протекает открывающий ток по цепи:

Upom - R33 - R34 - 6-э Q3 - "корпус".

Транзистор Q3 открыт до насыщения, а сигнал PG, снимаемый с его коллектора, имеет пассивный

низкий уровень и запрещает запуск процессора. За это время, в течение которого уровень напряжения на конденсаторе

С20 достигает уровня на резисторе R32, импульсный блок питания успевает надежно выйти в номинальный режим

работы, т.е. все его выходные напряжения появляются в полном объеме.

Как только напряжение на С20 превысит напряжение, снимаемое с R32, компаратор 4 переключится,

него выход ной транзистор откроется.

Это повлечет за собой закрывание транзистора Q3, и сигнал PG, снимаемый с его коллекторной

нагрузки R35, становится активным (Н-уровня) и разрешает запуск процессора.

При выключении импульсного блока питания из сети на вторичной обмотке пускового трансформатора

Т1 переменное напряжение исчезает. Поэтому напряжение на конденсаторе С19 быстро уменьшается из-за малой

емкости последнего (1 мкф). Как только падение напряжения на резисторе R25 станет меньше, чем на резисторе

R27, компаратор 3 переключится, и его выходной транзистор откроется. Это повлечет за собой защитное отключение

выходных напряжений управляющей микросхемы U4, т.к. откроется транзистор Q4. Кроме того, через открытый

выходной транзистор компаратора 3 начнется процесс ускоренной разрядки конденсатора С20 по цепи: (+)С20

- R61 - D14 - к-э выходного транзистора компаратора 3 - "корпус".

Как только уровень напряжения на С20 станет меньше, чем уровень напряжения на R32, компаратор

4 переключится, и его выходной транзистор закроется. Это повлечет за собой открывание транзистора Q3 и

переход сигнала PG в неактивный низкий уровень до того, как начнут недопустимо уменьшаться напряжения

на выходных шинах ИБП. Это приведет к инициализации сигнала системного сброса компьютера и к исходному

состоянию всей цифровой части компьютера.

Оба компаратора 3 и 4 схемы выработки сигнала PG охвачены положительными обратными связями

с помощью резисторов R28 и R60 соответственно, что ускоряет их переключение.

Плавный выход на режим в данном ИБП традиционно обеспечивается при помощи формирующей цепочки

С24, R41, подключенной к выводу 4 управляющей микросхемы U4. Остаточное напряжение на выводе 4, определяющее

максимально возможную длительность выходных импульсов, задается делителем R49, R41.

Питание двигателя вентилятора осуществляется напряжением с конденсатора С14 в канале выработки

напряжения -12В через дополнительный развязывающий Г-образный фильтр R16, С15.

Транзисторы, используемый в компьютерных импульсных блоках питания

Тип транзистора |

IK max, А |

Ur max

(Uкэ0

max, B |

Uкб0 max, В |

Pк max, Вт |

Tmax,°C |

h21э |

Режим измерения |

Iкб0,мкА |

fгр, МГц |

CK,пФ |

tсп,мкс |

Корпус |

Uкэ, В |

Iк, A |

2SC3320 |

15 |

400 |

600 |

100 |

- |

>10 |

6 |

5 |

- |

- |

- |

0-15 |

ТО-247 |

2SC3042 |

12 |

(400) |

500 |

2,5 |

140 |

15-50 |

5 |

0.8 |

10 |

20 |

- |

- |

ТО-218 |

2SC2625 |

10 |

400 |

650 |

100 |

- |

>10 |

2 |

5 |

- |

20 |

- |

1 |

ТО-247 |

2SC3318 |

10 |

400 |

600 |

100 |

- |

>10 |

2 |

5 |

— |

— |

— |

0.15 |

ТО-247 |

2SC3306 |

10 |

400 |

530 |

100 |

140 |

>10 |

5 |

5 |

0,1 |

- |

- |

1 |

ТО-247 |

MJE16080 |

8 |

400 |

800 |

100 |

140 |

15-25 |

- |

4 |

2500 |

20 |

- |

- |

ТО-220АВ |

2N6929 |

8 |

350 |

550 |

100 |

175 |

10-35 |

8 |

3 |

100 |

20 |

- |

- |

ТО-220АВ |

2SC3040 |

8 |

(400) |

500 |

2.5 |

140 |

15-50 |

5 |

0.8 |

10 |

20 |

- |

- |

ТО-218 |

2N6928 |

8 |

300 |

450 |

100 |

175 |

10-35 |

8 |

3 |

100 |

25 |

- |

- |

ТО-220АВ |

2SC3636 |

7 |

500 |

900 |

80 |

150 |

>8 |

0,8 |

5 |

10 |

- |

- |

0.2 |

SOT-93 (ТО-218) |

2SC3039 |

7 |

(400) |

500 |

1,7 |

140 |

15-50 |

5 |

0,8 |

10 |

20 |

- |

- |

ТО-220 |

2SC3039L |

7 |

(400) |

500 |

1.7 |

140 |

15-30 |

5 |

0.8 |

10 |

20 |

- |

- |

ТО-220 |

2SC3039M |

7 |

(400) |

500 |

1.6 |

140 |

20-30 |

5 |

0,8 |

10 |

20 |

- |

- |

ТО-220 |

2SC3039N |

7 |

(400) |

500 |

1,7 |

145 |

30-50 |

5 |

0,8 |

10 |

20 |

- |

- |

ТО-220 |

2SC3039 |

7 |

(400) |

500 |

1.7 |

140 |

15-50 |

5 |

0,8 |

10 |

20 |

- |

- |

ТО-220 |

2SC3039L |

7 |

(400) |

500 |

1.7 |

140 |

15-30 |

5 |

0,8 |

10 |

20 |

- |

- |

ТО-220 |

2SC2536 |

7 |

400 |

500 |

80 |

140 |

>20 |

0,1 |

5 |

100 |

- |

- |

1 |

SOT-93 (ТО-218) |

2SC4242 |

7 |

400 |

450 |

60 |

- |

210 |

40 |

5 |

- |

30 |

- |

1 |

ТО-220АВ |

2SC2305 |

7 |

400 |

400 |

80 |

140 |

>10 |

5 |

4 |

10 |

- |

- |

- |

SOT-93 (ТО-218) |

2SC3044A |

6 |

450 |

450 |

100 |

175 |

>10 |

3 |

5 |

10 |

30 |

- |

- |

ТО-220АВ |

2SC3755 |

5 |

800 |

1500 |

60 |

140 |

>8 |

1 |

5 |

10 |

- |

- |

0.3 |

SOT-93 (ТО-218) |

2SD1877 |

4 |

800 |

1500 |

50 |

140 |

3.5-7 |

2.5 |

5 |

10 |

20 |

- |

0.3 |

SOT-93 (ТО-218) |

2SD1883 |

4 |

800 |

1500 |

50 |

140 |

3.5-7 |

2.5 |

5 |

10 |

20 |

- |

0.3 |

SOT-93 (ТО-218) |

2SD1876 |

3 |

800 |

1500 |

50 |

145 |

3-6 |

2 |

5 |

10 |

25 |

- |

0.3 |

SOT-93 (ТО-218) |

2SC2378 |

0.1 |

(50) |

70 |

0.25 |

125 |

185 |

6 |

0.1 |

0.1 |

250 |

3 |

- |

ТО-92 (ТО-226АА) |

2SC945 |

0.1 |

50 |

60 |

0,25 |

125 |

200 |

6 |

0.001 |

0.1 |

250 |

3,5 |

- |

ТО-92 (ТО-226АА) |

2SC945RA |

0.1 |

(50) |

60 |

0.25 |

125 |

180 |

5 |

0,001 |

0.1 |

250 |

3 |

- |

ТО-92 (ТО-226АА) |

2SC945R |

0.1 |

(50) |

60 |

0.25 |

125 |

90 |

6 |

0,0013 |

0.1 |

250 |

3,5 |

- |

ТО-92 (ТО-226АА) |

2SC945PA |

0.1 |

(50) |

60 |

0,25 |

125 |

400 |

6 |

0.001 |

0,1 |

250 |

3 |

- |

ТО-92 (ТО-226АА) |

2SC945QA |

0.1 |

(50) |

60 |

0.25 |

125 |

270 |

6 |

0,001 |

0.1 |

250 |

3 |

- |

ТО-92 (ТО-226АА) |

2SC945P |

0.1 |

(50) |

60 |

0.25 |

125 |

200 |

6 |

0.001 |

0,1 |

250 |

3,5 |

- |

ТО-92 (ТО-226АА) |

2SC945Q |

0.1 |

(50) |

60 |

0,25 |

125 |

135 |

6 |

0.001 |

0.1 |

250 |

3.5 |

- |

ТО-92 (ТО-226АА) |

2SC945KA |

0.1 |

(50) |

60 |

0,25 |

125 |

600 |

6 |

0.001 |

0.1 |

250 |

3 |

- |

ТО-92 (ТО-226АА) |

2SC945LRA |

0.1 |

(50) |

60 |

0,25 |

125 |

180 |

6 |

0,001 |

0.1 |

250 |

3 |

- |

ТО-92 (ТО-226АА) |

2SC945K |

0.1 |

(50) |

60 |

0.25 |

125 |

300 |

6 |

0.001 |

0.1 |

250 |

3.5 |

- |

ТО-92 (ТО-226АА) |

КТ375А |

0.1 |

60 |

60 |

0.2 |

125 |

10-100 |

2 |

0.002 |

0.4 |

250 |

5 |

- |

ТО-92 (ТО-226АА) |

2SC1222E |

0,1 |

(50) |

60 |

0.25 |

125 |

350 |

6 |

0,001 |

0,05 |

250 |

3.5 |

- |

ТО-92 (ТО-226АА) |

2SC2308 |

0,1 |

(50) |

60 |

0.2 |

125 |

100 |

12 |

0.002 |

- |

230 |

- |

- |

ТО-92 (ТО-226АА) |

2SC1345D |

0.1 |

(50) |

55 |

0.2 |

125 |

250 |

12 |

0.002 |

0.5 |

230 |

3.5 |

- |

ТО-92 (ТО-226АА) |

2SC1570F |

0.1 |

(50) |

55 |

0.2 |

125 |

160 |

6 |

0.001 |

0,1 |

100 |

- |

- |

ТО-92 (ТО-226АА) |

2SC641KC |

0.1 |

(15) |

40 |

0.1 |

125 |

80 |

5 |

0,001 |

0.25 |

400 |

0.9 |

- |

ТО-92 (ТО-226АА) |

2SC2026 |

0.05 |

(14) |

30 |

0,25 |

150 |

80 |

10 |

0.01 |

0.1 |

1500 |

0.75 |

- |

ТО-92 (ТО-226АА) |

2SC2037 |

0,05 |

(14) |

30 |

0.25 |

150 |

80 |

10 |

0.01 |

0,1 |

1500 |

0.75 |

- |

ТО-92

(ТО-226АА) |

Адрес администрации сайта: admin@soundbarrel.ru

|